2023 Edition

# **Chapter 16: Emerging Research Devices**

For updates, visit <a href="http://eps.ieee.org/hir">http://eps.ieee.org/hir</a>

The HIR is devised and intended for technology assessment only and is without regard to any commercial considerations pertaining to individual products or equipment.

We acknowledge with gratitude the use of material and figures in this Roadmap that are excerpted from original sources. Figures & tables should be re-used only with the permission of the original source.

## **Table of Contents**

- Chapter 1: Heterogeneous Integration Roadmap: Driving Force for Systems of the Future

- Chapter 2: High Performance Computing and Data Centers

- Chapter 3: Heterogeneous Integration for the Internet of Things (IoT)

- Chapter 4: Medical, Health and Wearables

- Chapter 5: Automotive

- Chapter 6: Aerospace and Defense

- Chapter 7: Mobile

- Chapter 8: Single Chip and Multi Chip Integration

- Chapter 9: Integrated Photonics

- Chapter 10: Integrated Power Electronics

- Chapter 11: MEMS and Sensor Integration

- Chapter 12: 5G, RF and Analog Mixed Signal

- Chapter 13: Co-Design

- Chapter 14: Modeling and Simulation

- Chapter 15: Materials and Emerging Research Materials

Chapter 16: Emerging Research Devices \_\_\_\_\_\_1

- 3. Printed Electronics 14

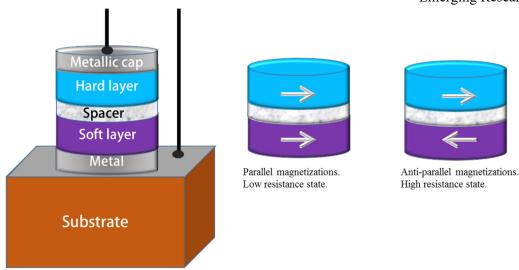

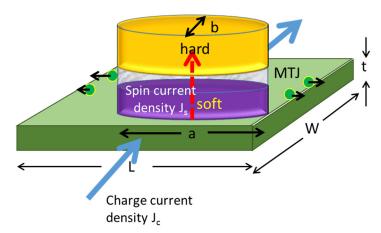

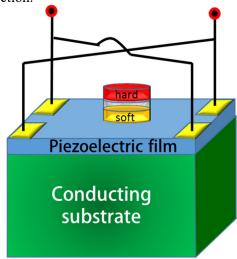

4. Spintronic Devices 19

- Chapter 17: Test Technology

- Chapter 18: Supply Chain

- Chapter 19: Cyber Security

- Chapter 20: Thermal

- Chapter 21: SiP and Module

- Chapter 22: Interconnects for 2D and 3D Architectures

- Chapter 23: Wafer-Level Packaging, Fan-in and Fan-out

- Chapter 24: Reliability

# **Chapter 16: Emerging Research Devices**

## **Executive Summary**

Information technology has relied upon scaling CMOS to maintain the pace of progress since it was introduced in 1963. The approaching economic end of Moore's Law is slowing that pace of progress. Although scaling of CMOS continues, the benefits are reduced as we Send corrections, comments and suggested updates to the TWG chair, using our HIR SmartSheet:

https://rebrand.ly/HIR-feedback

approach the limits of the physics for these devices. The historical benefits of lower cost, lower power, smaller size and weight, higher functional density and higher performance are reduced and, in some cases, no longer available. We are now experiencing a dramatic increase in research and development to find new devices to replace CMOS for memory and logic applications.

There have been many new candidate devices and materials introduced in recent years, but most are still in the early stages of development. The objective of this chapter is to identify new device types that hold the promise of maintaining or accelerating the pace of progress over the next 25 years, and the difficult challenges that must be overcome to realize that potential.

The increasing penetration of high-performance electronics into mobile consumer devices is resulting in a rapidly growing number of product types. These products typically have lower unit volume and shorter product life cycle than traditional computer components. Device design and engineering cost, at the same time, is rising rapidly as we approach the limit of the physics. Thus, time to market and non-recurring engineering cost will be critical challenges to overcome for emerging research devices.

We have achieved 50 years of progress through evolutionary change that has led to information technology penetrating every phase of our lives. This is no longer possible. The future must embrace revolutionary change in devices and materials if we are to maintain our historical pace of progress.

#### Introduction

Dimensional scaling that has been going on for more than five decades is reaching its fundamental limits. Continued gain in device speed while lowering power consumption is increasingly difficult. These factors together have created the urgent need to explore new devices for information processing and memory, new architectures, and new approaches for heterogeneous integration of existing functions for emerging applications.

The scope of this Chapter includes supporting other HIR Working Groups with new devices required to meet the difficult challenges they identify and assessing the emerging research devices and technologies for this purpose. Table 1 below lists Emerging Research Device types known today. However, the most important devices over the next 25 years are likely to be the types that we have not yet imagined.

Table 1: Candidate emerging research devices

| Nanoscale vacuum electronics                                                        |

|-------------------------------------------------------------------------------------|

| Neuromorphic devices                                                                |

| Quantum devices for information processing                                          |

| Spintronic devices                                                                  |

| Flexible electronics                                                                |

| 3 dimensional stacked devices                                                       |

| Nanowire electronics                                                                |

| Carbon nanotube electronics                                                         |

| Graphene electronics                                                                |

| Other 2D material-based electronics                                                 |

| Plasmonic devices                                                                   |

| Power electronics                                                                   |

| Electronics for harsh environment – automotive, industrial, space                   |

| Electronics for harsh environment – extreme temperature, radiation, vibration, etc. |

| New MEMS and Sensors both as components and integrated into sub-systems             |

| Phase change memory (both thin film and nanowire-based)                             |

| Resistive random-access memory (both thin film and nanowire based)                  |

| Ferroelectric memory                                                                |

| NEMS based memory                                                                   |

| Molecular memory                                                                    |

This HIR 2023 edition includes examples for seven of the device types listed in table 1 that are already emerging as candidates to replace CMOS in specific applications. This includes a section dealing with printed electronics which can provide a cost-effective solution for low-volume product with reduced non-recurring engineering. It also shows promise for printing living tissue, relying upon cellular self-assembly to obtain bio-printed living tissue<sup>1</sup>:

- Nanoscale Vacuum Electronics

- Neuromorphic Devices

- Printed Electronics

- Spintronic Devices

- Graphene and 2D Material Electronics

- Carbon Nanotube Electronics

- Plasmonic Devices

#### 1. Nanoscale Vacuum Electronics

Vacuum electronics potentially offers unique advantages over semiconductor electronics in speed, power and resistance to damage by extreme environments such as radiation and high temperature [1-4]. Reducing the critical dimensions and fabrication using modern IC manufacturing techniques including extreme UV (EUV) lithography can bring vacuum electronics into the sub-10 nm nanoscale era. These advantages, however, have not yet been realized, and much remains to be understood to enable more efficient operation at the component level and integration into circuits. The device performance (e.g. drive current vs. voltage) is governed by the following fundamental processes: emission from the cathode; transport in a nano-vacuum channel; and collection by the anode.

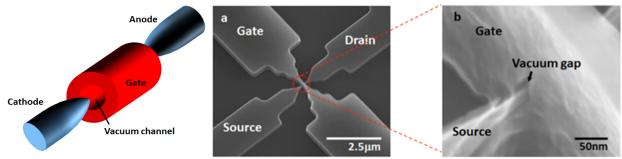

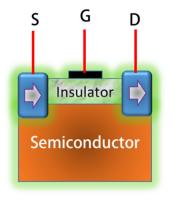

Preliminary efforts [1] in this area have produced nanoscale vacuum channel transistors with a source-to-drain distance of less than 50 nm and a surround gate, as shown in Figure 1. The device operated under a drain voltage of 2 V and a gate bias below 5 V, providing a drive current of 3  $\mu$ A. Entirely silicon-processing steps were followed on a 200 mm wafer. Since the mean free path at atmospheric pressure is tens of micrometers, which is a few orders of magnitude larger than the channel dimension, no vacuum was used. The device performance was found to be robust against high temperature and ionizing radiation. A similar effort [2] on 150 mm SiC wafers, but for a vertical structure with the source at the bottom and drain at the top, proved equally successful. The surround gate in both cases provided excellent electrostatic control. These early demonstrations of wafer-scale fabrication appear to be promising for the future of miniaturizing vacuum devices into the nanoscale.

Figure 1: Schematic of a silicon nanoscale vacuum channel transistor with a surround gate, and SEM images of the fabricated device [1]

Vacuum electronics does not have complementary devices working in pairs as in the case of CMOS and thus, the low standby power consumption and high noise immunity common in CMOS technology is missing in vacuum electronics. Recently, a proposal has been made [5] to construct complementary vacuum devices by combining field emission with nanoelectromechanical (NEM) actuation of the gate.

One of the main limitations of nanoscale vacuum channel transistors (NVCTs) is their low transconductance. The small intrinsic gain is attributed to the limited current density. Despite the fact that vacuum is ideal as carrier transport medium, the tunneling resistance at the emitter-vacuum interface largely limits the emission current. The emission current is determined by the energy barrier and electric field on the cathode surface. The surface field needs to be at least  $\sim$ 1 GV/m for significant emission. The channel current has been significantly improved in the past decade by reducing the gap size to  $\sim$ 10 nm range and/or by modifying the work function of the emitter surface. Reducing the

<sup>&</sup>lt;sup>1</sup> American Institute of Physics June 4, 2019 issue of Applied Physics Reviews, from AIP Publishing

gap size naturally results in reducing the operating voltage, and less than 5 V operation has been demonstrated. Despite these improvements, the transconductance still remains one or two orders of magnitude smaller than those of CMOS transistors.

The maximum obtainable current of a vacuum FET is ultimately limited by the Child-Langmuir (C-L) law, which dictates a 1/(gap)²-dependence of channel current. Theoretically, the gap size can be reduced to the direct tunneling regime (~2 nm). Extremely scaled channel length can shorten the carrier transit time. Down-scaling the gap size will continue to increase the current, but still the upper bound of the channel current is set by this C-L limit, which is caused by the space charge effect of electrons in transit. Another limitation of vacuum electronics at circuit level is the unavailability of CMOS-like circuits that will minimize static power consumption. Other challenges include finite output impedance, long-term reliability, and lack of fundamental models and simulators, especially for the sub-10 nm regime.

The ageing model needs to be understood for long-term reliability. The long-term degradation behavior of vacuum electronics devices is different from that of sold-state electronic devices due to differences in the underlying mechanism. Degradation mechanisms in vacuum devices include atomic migration near the cathode, whisker growth, gas leak into the vacuum channel, ion bombardment due to residual gas, and phase shift of material. The acceleration stress test methods need to be standardized.

For the cathode, a mechanically and chemically robust yet sharp needle-like tip is preferred. The top-down fashioned fabrication from bulk semiconductor crystal may cause variability in terms of such demand. A hybrid of top-down fabrication as baseline and bottom-up growth of 1D/2D nanotube/nanowire/nanosheet for the cathode could be a solution.

Difficult challenges and potential solutions include:

# 5-year horizon:

- Manufacturing of nano-gap beyond 10 nm: precise control of gap size is critically important for reproducible device characteristics.

- Solutions: advanced nanopatterning techniques, bottom up self-assembly or epitaxial regrowth of electrode, leveraging advanced lithography such as double- and quadruple-patterning, hybridizing with 1D or 2D materials.

- Related issue: roughness of the emitter surface: the surface roughness at ~10-nm-scale gap sensitively affects emission current via an atomic scale geometric (field enhancement) and/or gap-size effect.

- Solutions: improvements in manufacturing process, electrode surface coating technology, exploration of new materials with inherently uniform outer surface at atomic scale (eg. 2D material), exploration of new materials with high (chemical and mechanical) robustness against bombardment.

- Overcoming the Child-Langmuir's space-charge-limit of channel current.

- Solutions: employ a space-charge neutralization concept; incorporate electron-transparent conducting (or semiconducting) 2D material (such as monolayer graphene) into the void channel toward the anode side; update Child-Langmuir model to take into account the phenomena of charge transport at sub-10 nm scale.

- Low-voltage operation (<~1 V) with enhanced channel current: important for low-power integrated circuits.

- Solutions: negative work function material, heterostructured superlattice, employ the 2D electron-gas (2DEG) effect at channel edge (low-voltage emission of electrons and ballistic transport in a nano-void channel).

- Solutions: employ a plasmonic effect for photo-enhanced emission of electrons at the cathode.

## 15-year horizon:

- Developing CMOS-like circuits for low standby power.

- Solutions: incorporate a tunnel FET as a conjugate form of vacuum FET; pair a p-channel V-FET with an n-channel T-FET.

- Developing THz-range vacuum transistors and circuits.

- Solutions: Explore novel pathways for implementing circuits in the absence of complementary devices.

#### Reliability, Packaging and Lifetime

Gated Field Emission Arrays (GFEAs) and individual gated emitters have been considered for a range of applications over the last few decades. Numerous companies pursued GFEAs for use in Field Emission Displays (FEDs) in the 1990's to early 2000's. The first FED was demonstrated by LETI-CEA in Grenoble, France. While companies pursuing FEDs had some technical successes, costs and the substantial gains in Liquid Crystal Display

technologies ultimately prevented any meaningful applications of FEDs. Because most of this work was performed in industry, little of that technological development has been published, and so many of the successes in reliability, lifetime performance, and vacuum packaging are little known outside these groups. As gated emitters are now being considered for vacuum transistors, some of the same issues that were studied in FED development are still a concern, and therefore a summary of what we know from FED development is given below.

## Reliability

One of the major concerns with GFEAs is reliability. Much of the published work comes from universities and laboratories and not from the companies that developed FEDs. The failure mechanisms in these structures occur from poor dielectrics or defects in the structure, surface breakdown, or emitter tip failure. Proper processing and design can prevent the first problem, and in company fab facilities, these types of structures can be reliably fabricated without significant defects. Such is not usually the case at university facilities; hence these devices often suffer from a number of reliability issues related to fabrication quality and not the inherent problems of the GFEAs. It is important to note that FEDs often had current requirements that were low (<100 mA/cm²), which does make it easier to develop. Once these process problems are resolved, tip arcing and breakdown becomes the major problem.

A team with LET-CEA and Texas Instruments published some details on the use of ballast resistors to limit current to the emitter tips and prevent arcs [6]. This approach served three purposes: (1) limiting the current to the tips, (2) improving uniformity of emission across the FED, and (3) providing a small built-in lifetime with the voltage drop across the resistor. When the resistors are large enough to provide current limit, there is insufficient charge to allow the excursion to a cathodic vacuum arc [7-9]. The resistance value and placement of the resistor are critical. It is preferable that the resistor be large enough that during typical operation there is a voltage drop across the resistor that is already limiting current, e.g., a 3 V drop for a 70 V gate to emitter drive signal. This level of voltage drop provides current limit and improves uniformity. It was found that for molybdenum field emitter tips operating with an average current of 3-5 nA, a resistor value around 1 G $\Omega$  provided the needed ballast. However, the resistor must be close to the tip in an array. If the resistor is far away from an array of tips, the gate to emitter capacitance might provide enough stored charge to allow the arc to still occur even though the resistor might limit the severity [9]. The arc initiates in < 1 ns, so the stored charge available must be small enough to limit the current to << 0.1 A. Hence, a key to emitter tip reliability is resistance or a limitation in available charge to prevent the arc from initiating. In the lifetime study of 5.2" diagonal FEDs fabricated at PixTech, the use of the ballast resistors (sputtered polysilicon thin film layer) allowed for FED operations >10,000 hrs. Rarely was emitter tip arc damage found on de-packaged displays.

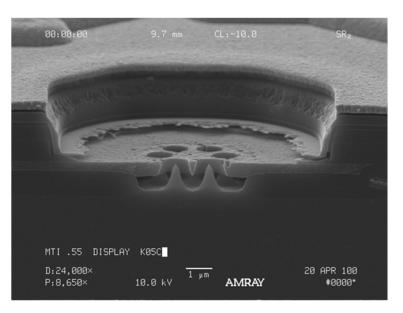

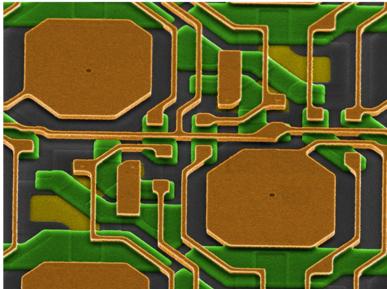

At Micron technology, 0.55" diagonal, active-matrix FEDs using silicon tips were fabricated almost entirely in a 200 mm silicon wafer DRAM memory fab. These displays eventually yielded well across the wafer and were extremely reliable. Because of the quality of the fabrication facilities and the engineering support, processes such as silicon tip etch and CMP were very stable. The active-matrix circuitry included several NMOS transistors to control emission current at the pixel (6-8 tips), a row address line, and a switched-capacitor charge control circuit. The switched-capacitor circuit then limits the current to the emitter tips. SEM images of the tip structures (cross section) and pixel layout (using false colors) are shown in Fig. 2. These devices were packaged to form FEDs and operated full-on (white screen) for ~40,000 hrs. and no arcs were identified, but it should be noted that not all of these packages were de-processed for study.

Therefore, tip reliability can be achieved by providing a mechanism that limits the current to such a level that the arc cannot initiate (<<0.1 A per emitter tip). This approach requires a process flow that can accommodate the ballast resistors or control circuitry. The problem with the resistors, of course, is that they also may limit temporal response for the application.

## **Packaging**

One of the concerns in the renewed interest of GFEAs is vacuum packaging, if the transistors operate at anything other than atmospheric pressure. There is a concern that the packaging technology is unreliable and costly despite progress particularly with MEMS devices. The major vacuum packaging issue for FEDs was the use of glass. The thin glass needed for flat displays made the packing process very challenging. Utilizing the technologies developed in the CRT and vacuum fluorescent display areas, most FED companies pursued the standard approach of using glass frits and getters to seal and pump the displays. The processes developed depended upon the chosen glass type and the seal process. There are basically two sealing approaches: vacuum sealing and exhaust sealing.

In exhaust sealing, the glass package is assembled and fired in either vacuum or gas (usually nitrogen) to prevent oxidation. Such sealing of glass in FEDs was usually performed around 500 deg. C depending upon the glass and the type of glass frit. For example, the PixTech FED GFEA cathodes were fabricated on glass substrates, the same type of glass used by LCD manufacturers (aluminosilicate) during the 1990s. After scribing the glass to form each display cathode, the cathode and anode (phosphor screen) were aligned and fritted together. Usually, the frit is dispensed on the anode. Weights or clamps cause the frit to extrude during heating forming the seal (~500 deg. C). Spacers (glass beads or rods) separate the anode from the cathode to form the vacuum gap. PixTech offset the entire structure to leave a "getter box" that was attached, using frit, to the end of the display. This box had an opening to place the getters. After firing in the oven or belt furnace, two types of getters were placed in the box through the hole. One was a non-evaporable getter (NEG) that is activated by temperature during seal under vacuum. The other was an evaporable getter that is "flashed" using inductive coupling after seal. This type of flashed getter is often visible in the exhaust tubes in CRTs. In the final seal process, a glass cap was placed over the hole in the getter box. This cap also had frit to form a seal. During the final seal, the entire package was heated to ~400 deg. C under vacuum. This heating caused the frit on the cap to soften and extrude, but the frit that was fired during the first package fire process did not soften. One critical step, known by display and microwave vacuum device manufacturers, is that water vapor must be baked out of the package prior to final seal. Typically, a temperature around 350 to 370 deg. C is used [10] with the

Figure 2. SEM images of the Micron 0.55" FED cathode (top) silicon tips in cross section forming 1 pixel and (bottom) false color image showing the layout of the active matrix circuitry showing several pixels but each has only 1 emitter tip.

package or components under vacuum. This is often performed with a soak at temperature from 6-15 hrs. depending upon the process. Once the soak has desorbed the water vapor, the temperature is increased to  $\sim$ 400 deg. C to seal off the package with the glass cap. The seal temperature activated the NEG. The evaporable getter is activated after the package is removed from the seal oven.

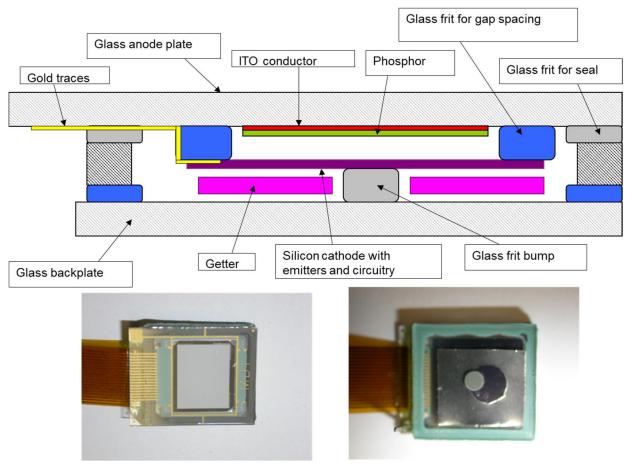

Micron Technology used a different approach. The 0.55" FED cathode was fabricated on silicon. Hence, the package had three components: the silicon cathode, the phosphor screen on glass, and a back plate assembled from glass. A pictorial representation and photographs of a monochrome display package (front and back) are shown in Fig. 3. In this process the back plate was assembled and formed using a frit that fired at 700 deg. C. This back plate formed the holding location for the NEG. The cathode was aligned and flip-chip bonded to the phosphor screen, which had "rails" on the edges to form spacers and make electrical connections. In these displays a 60 µm anode to cathode vacuum gap was used with an anode voltage of 1400-1600 V. In this approach the getter adsorbed gases from its location on the backside of the cathode. A glass frit that fired at ~400 deg. C was dispensed on the back plate. Then the anode, with cathode attached, was assembled to the back plate using a spring clip to hold the backplate against the anode. This entire assembly was placed in a vacuum furnace. The furnace was ramped to 360 deg. C

under vacuum to cause water desorption, and then after 8-10 hrs. the temperature was raised to 400 deg. C. At this point the glass frit on the anode extruded, sealing off the package. Note that no exhaust port or opening for exhaust was needed. Gas was pumped from the package through the gaps formed by the variation in the glass frit and its contact to the anode. To ensure this, slight bumps in the frit were often purposely created at the corners of the frit bead. The seal temperature again activated the NEG. The 0.55" FEDs and 5.2" FEDs were tested nearly 20 years after being sealed and were still operational.

This entire "back-end" process for the 0.55" FED was automated. The silicon wafers were coated with photoresist to protect the emitter tips from particles during sawing. After sawing, the cathode die were picked and placed in boats for resist strip. Pick and place tools took the phosphor screens and placed them in boats. The cathodes were flip-chip bonded to the screens. Back plates were then placed on the phosphor screens in the boats. A spring clip was placed on the back plate and connected to the boat to provide the sealing force. Five FED packages were assembled per boat. Five boats were placed into a cassette, and these cassettes (4-5) were placed in the vacuum furnace for seal. After seal, the cassettes were unloaded, and each boat was placed in a test machine to turn on and check the displays. Good displays were connected with flex tape and sent to a burn-in tool on boards for 48 hrs. of testing followed by final display test. Hence, this packaging lends itself to low-cost batch processing.

Figure 3. (Top) pictorial representation of the 0.55" FED package showing back plate, cathode, phosphor screen, and getter and (bottom) front and back photographs of the package showing the white phosphor, the flex tape, the frit seal, and the getter (metal with hole punched out).

#### Lifetime

Once reliable devices are achieved and packaged, lifetime testing begins. While vacuum chamber testing is a good starting point, most development requires testing of dozens to hundreds of devices in vacuum packages. The minimum testing time should be 1000 hrs. to get an understanding of the device performance. In this discussion, we are considering packaged FEDs as mentioned above. Oxidation appears to be the primary cause of emitter tip degradation for both silicon and molybdenum tips [11]. The tips are extremely sensitive to oxidation. For example, heating the silicon tips to 400 deg. C in air for 5 min caused degradation in the 0.55" packaging process discussed above. The performance could be recovered by dipping the silicon tip FED cathode in a buffered HF to remove

silicon dioxide. It was also found that operation in a vacuum test chamber with a phosphor screen caused degradation with the same effect when treated with HF. Moly tips also showed rapid oxidation from the phosphor screens. Vacuum baking could recover the tips. Hence, no permanent damage to the tips (Si or Mo) was ever identified during lifetime testing. The performance was always found to be recoverable. Even metal anodes have an oxide layer, and over hundreds of hours, these anodes caused degradations.

Two methods were implemented to reduce the oxygen content on the phosphor screen. In one case, the phosphor screens were "electron scrubbed" to reduce the surface of the phosphor, depleting the impact surface of oxygen. This approach allowed the 0.55" FEDs with silicon tips to achieve 40,000 hrs. of operation for approximately 20 displays. Electron scrubbing was also used on the 5.2" passive matrix FEDs. This approached improved the degradation (50% reduction in current) from hundreds to many thousands of hours. Dozens of displays were tested to demonstrate this effect. The second approach was applied to 7" color FEDs developed at PixTech. These FEDs worked at 3-5 kV on the phosphor screen. Here, a thin aluminum layer was used to improve efficiency, similar to the process in CRTs, but the oxide on the aluminum surface still degraded the emitters. PixTech engineers developed a very thin (<0.06 µm) aluminum nitride layer. Because this layer was low in oxygen, lifetimes improved from hundreds of hours to  $\sim 10,000$  hrs.

Hence, the primary degradation mechanism for tips is oxygen liberated from the anode, but the implementation of solutions depends upon applications. FEDs have anodes that vary in bias from 200 V to 10,000 V. It is not clear how the lower anode voltage (< 50 V) in vacuum transistors may affect this oxygen liberation from the anode. It should also be noted that FEDs were not operated past 40,000 hrs. and there was some current degradation. Therefore, other degradation mechanisms are possible.

#### References

- 1. J.W. Han, et al., Nanoscale vacuum channel transistors, Nano Lett. 17, pp. 2146-2151 (2017).

- 2. J.W. Han et al., Nanoscale vacuum channel transistors fabricated on silicon carbide wafers, Nature Electronics, 2, pp. 405-411 (2019).

- 3. S. Srisonphan, Y.S. Jung and H.K. Kim, Metal-oxide-semiconductor field-effect-transistor with a vacuum channel, Nature Nanotechnology, 7, pp. 504-508 (2012).

- 4. S. Niirantar, T. Ahmed, G. Ren, P. Gutruf, M. Bhaskaran, S. Walia and S. Sriram, Metal-air transistors: semiconductor-free field-emission air-channel nanoelectronics, Nano Lett. 18, pp. 7478-7484 (2018).

- 5. R. Bhattacharya, J.W. Han et al., Complementary vacuum field emission transistor, IEEE Trans. Electron Devices, 68, pp. 5244-5249, 2021.

- 6. J. D. Levine, R. Meyer, R. Baptist, T. E. Felter, and A. A. Talin, Field emission from microtip test arrays using resistor stabilization, J. Vac. Sci. Technol. B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena 13, 474, 1995; https://doi.org/10.1116/1.588336

- 7. M. Gilmore, N. E. McGruer, J. Browning, and W. J. Bintz, Measurement of Gated Field Emitter Failures, Rev. Scientific Instruments, 64, pp. 581-582, 1993. https://doi.org/10.1063/1.1144181

- 8. J. Browning, S. Meassick, Z. Xia, C. Chan, and N. McGruer, Ion and electron energies in gated field emitter failures, IEEE Trans. Plasma Sci., 21, pp. 259-260, 1993. DOI: 10.1109/27.219398

- 9. J. Browning, N. McGruer, S. Meassick, C. Chan, W. Bintz, and M. Gilmore, Gated Field Emitter Failures: Experiment and Theory, IEEE Trans. Plasma Sci., 20, pp. 499-506, 1992. DOI: 10.1109/27.163587

- 10 R. Bhattacharya, N. Karaulac, W, Chern, A.I Akinwande, and J. Browning, Temperature effects on gated silicon field emission array performance, J. Vac. Sci. Technol. B 39, 023201, 2021; https://doi.org/10.1116/6.0000753

- 11. B. R. Chalamala, R. M. Wallace, and B. E. Gnade, Effect of O<sub>2</sub> on the electron emission characteristics of active molybdenum field emission cathode arrays, J. Vac. Sci. Technol. B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena 16, 2859, 1998; https://doi.org/10.1116/1.590285.

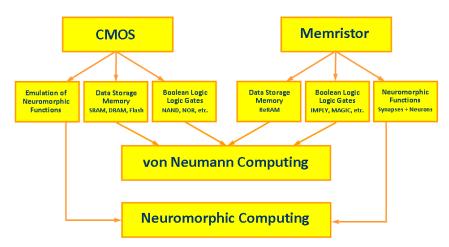

# 2. Neuromorphic Devices

As digital CMOS scales to dimensions in the 7-5 nm range, the cost increase per generation has outstripped the shrinkage factor, which defeats the benefits Moore's Law. The cost per unit area is increasing for each new generation. Secondly, the power consumption for massively scaled devices has become significant, which makes their usage in mobile devices unattractive. Beginning at about the 65nm node, passive power has often exceeded active power. Third, packaging technology has not proceeded at pace with chip technology. Fourth, although not directly related to devices, EDA tools – because of the increasing complexity of design rules, the scale of integration and the multiplying reliability checks required have made the cost and time to design and verify chips skyrocket. Fifth, interconnect technology continues to be a challenge, including contact resistance, as the impedance of chiplevel interconnects scale in the wrong direction. Sixth, yield at the wafer level will be low, raising the cost of the

system. These problems are multiplied at the wafer scale. And from a power and yield consideration, they are prohibitive.

## **Background and Overview**

The key concept motivating neuromorphic devices is that one can use the brain as a model for a computer. This is a pure biomimetic approach. In the human brain, higher-level information processing occurs in the neo-cortex. Neurons work together to interpret sensory data (input) to produce cognition, spatial reasoning, planning and generation of motor commands and language (output). Different parts of the neo-cortex specialize in one or more specific processing tasks but do so in concert with the other parts. The wiring of the brain consists of some 86 billion neurons, each of which is connected in a massively parallel network to tens of thousands of other neurons. If the combination of incoming signals received by a neuron from other neurons raises its input voltage past a certain threshold, voltage-gated ion channels begin to open, which then transmit an electro-chemical signal to multiple other neurons. The signal can be either excitatory or inhibitory. Thus, many millions of neurons are active (firing) at any one time, whereas many billions are quiescent. One can then pattern a heterogeneous integration scheme by building discrete devices, each mimicking the principal function of one part of the neo-cortex while interconnected to the others.

Neuroscientists used to believe that learning occurred solely in the synapses, whereby they interpret signals from axons and retransmit them via dendrites to neurons. The current wisdom is that learning comes about primarily by the creation of new synapses (synaptic plasticity). Up to 40% of synapses transmitting to a neuron changes daily.[1] This is how new things are learned without interfering with prior knowledge.

Dendrites are not just bits of wire. They also have their own apparatus for making spikes. If enough inputs are activated in the same small bit of dendrite, then the sum of those simultaneous inputs will be larger than the sum of each input acting alone. This is non-linear behavior. Each dendrite from a neuron can integrate inputs, then output a spike, which means that each branch of a dendrite acts like a little nonlinear output device, summing up and outputting a local spike if that branch gets enough inputs at roughly the same time. The neuron then collects all these non-linear inputs and responds. It only responds when a lot of the inputs are active together in time and in space (on the same bit of dendrite). It cannot detect anything that is not a local spike, which means that it ignores most of its individual inputs. (It is not understood how remote signals that trigger motor responses connect). So the neurons respond only to a small fraction of the information they receive, with the rest tucked away in their dendrites. That is, it acts as a kind of processor, which means to say that it is its own little computer, but not the traditional kind, since the inputs are not binary and the output is more a result of a weighted polling than an arithmetic summing.

Computers represent data in a brittle fashion. If one bit flips and there is no error correction, an error is produced. The brain, on the other hand, uses sparse representation of data where relatively few neurons are active at one time, even though it takes thousands of signals to stimulate a single neuron. This is what really enables understanding, thinking and planning, since individual signals can overlap, producing generalized patterns. The signals can also combine, which allows multiple ideas to exist simultaneously, permitting the brain to handle uncertainty relatively easily.

In the neo-cortex, sensory data is processed in a hierarchy of its parts. When the brain attempts to recognize a pattern, an input is passed from one part to another and as it does, it gains more complex levels of extraction as each part represents a different sensory-motor experience. At the end of the process, a pattern is recognized. That is, the recognition is not simply by sound or image or touch but by all these integrated together. A computer attempts to emulate this behavior when designed to implement deep learning schemes, but does so much less efficiently and accurately and with many more deep layers than used by the brain.

A neuron has an average electric potential of about 70mV [2], which changes when it receives signals from other neurons. It will then spike when this membrane voltage reaches a certain threshold. The spike or pulse has a width of a few ms and a height of about 40mV. It can be transformed when it reaches a synapse before being transmitted down connecting dendrites to other neurons. The energy cost of creating an electric potential in a synapse is about 10fJ [3]. The gate of a MOS transistor used in state-of-the-art CPUs is about 0.5fJ. At the cell level, a neuron matches neither the speed nor the low energy of a modern transistor switch. On the other hand, the power expended during a synapse is five orders of magnitude less than that of a switching transistor because it is two million times slower. At the chip level, when transistors are used to simulate a brain function with a similar sized portion as that of the brain, the power consumption is 10 billion times larger and is less accurate [4]. The clear point here is that the key to achieving brain-like power consumption will not be achieved by the device per se but rather by the chip architecture and design. This will be aided by changing how the device is operated.

So, what makes the brain so much more efficient than computers? What will it take to make super computers operate at 20w, as the brain does? Here are some of the key differences. The brain transmits spikes that are binary. It retains the nice feature of digital electronics in that it can transmit a signal a long way without loss of integrity and is refreshed at every synapse. On the other hand, it really is a mixed-signal organ in that inputs to neurons are weighted. If it were a transistor, many of the signals would be sub-threshold. Second, there are no clocks. Everything works asynchronously, with actions triggered locally. Some digital designs today also use asynchronous clock trees. The difference is a massive difference in parallelism and in its mode of operation. Only 1-2% of the neurons in the neo-cortex are firing at any one time [1]. Third, operations are highly local. Ninety percent of neurons only connect to a thousand or so neighbors such that the average lengths of axons and dendrites are short compared to the size of the brain. The brain does not require global interconnects. It does require a global blood supply and lymphatic system. There is a need to connect remote areas of the brain when, for example, a motor reflex is needed in response to a visual queue, but this function of the brain is not understood since there does not appear to be an observable global, physical connection. Fourth, a synapse retains and remembers its state even when not active. Fifth, a neuron is able to branch in three dimensions. Sixth, memory elements are not separate from signal processing elements. There are no CPUs or bus lines.

## Difficult challenges for the technical issue

The first issue to confront is the chicken-and-egg problem of what comes first. Is it the device, or the architecture and design? Experience teaches us that it is best to develop and optimize the device in parallel and iteratively with the architecture. As explained before, the major gain to be realized in power reduction will come from the architecture, algorithms and design more so than from the device. In fact, the device will almost certainly be more than one device (neuron and synapse) and each device could be a cell made of several components rather than a single component. On the other hand, the component and cell designs will enable the architecture.

A straightforward way to resolve the chicken-and-egg question is to select an application. An application requires a design specification, which, in turn, sets requirements for the components, which, in turn, highlights the attributes that need improvement. It is a key enabler. Neuromorphic chips are not particularly good at number processing, but excel in applications which feature processing of continuous sensory inputs. A natural choice for an application might be an AI/deep learning task. Today, there does not appear to be any neuromorphic design that does the job as well as other alternatives. A first step would be to demonstrate a chip that is superior in power, cost or accuracy to an existing design, followed by its incorporation into a HI design as a second step.

Speech and facial pattern recognition are accomplished in the cloud using high-powered servers. A target application might be to replace this server function with a lower power version, one that perhaps uses far fewer hidden layers. The brain does the job with as few as four, whereas a deep learning app may require a hundred layers. A more aggressive target might be to replace the server function entirely by putting a neuromorphic chip in a mobile device.

Without HI, the application will require standard and complex I/Os as well as ESD cells which are all obtainable, since standard components are envisioned. However, in a wafer-scale HI application where one neuromorphic chip communicates with another, analog signals may be all that are necessary.

Finally, work needs to be done to improve the control of transistors in sub-threshold operation. Small changes in gate voltage result in large changes in drain current, which make chips prone to failure. The problem is a yield challenge as well as a reliability challenge, as devices burn-in with use causing sensitive parameters to shift during the device lifetime.

## Requirements for key attributes over time

We need a cell design that imitates a neuron soma and one that imitates a synapse. We need a transistor that operates reliably and predictably in the sub-threshold region. We do not need an ultra-fast transistor, since the processing speed of a neuromorphic circuit will depend upon parallelism, and it is advantageous to have a low-leakage cell, which is more easily attainable if deep submicron technology is not used. Ultra-fast transistors that are underdriven can reduce active power but less so passive power. In this same regard, a sub-threshold slope below the theoretical limit for bulk Si (60mv/decade) would be an advantage. We need a cell or a component that is non-volatile. We need a cell with one input and one output (synapse) and another cell with hundreds to thousands of inputs and outputs (neuron). We need 3D technology to facilitate massive use of local interconnects. We need the technology that will interconnect the HI chips and control the signals. This includes the controller chip as well as the interconnect hardware (interposers, etc).

The Gordian Knot that must be cut is that there are no quantified targets with acceptable tolerances defined for the required components. These depend upon the "final" architecture that will be used to implement a purely biomimetic

system. Since there is no consensus system architecture, there cannot be a well-defined, quantitative list of performance metrics. Without device performance metrics, a fully neural architecture cannot be designed. Key to resolving this issue is picking a flagship application that is suitable for a neuromorphic solution and proceeding iteratively with an architecture/circuit design/PCD project. This will have the benefit of spurring model development and EDA tools.

#### **Potential Solutions**

Several groups have been pursuing neuromorphic systems for several years. The SpiNNaker project[5] at the University of Manchester attempts to imitate spikes by using massively parallel ARM9 processors to route them asynchronously. The latest version uses 57,600 processors, each with eighteen cores and each of these simulating as many as a thousand neurons. A prototype chip has been recently designed with a second generation SpiNNaker system [24] that demonstrates efficient execution of brain-inspired algorithms, specifically a reward-based synoptic sampling model that employs structural plasticity to learn a function or a task. This simulation of a synapse is clearly a brain-inspired algorithm. It is sponsored by the EU's Human Brain Project. The Human Brain Project also sponsored the BrainScaleS Project [6] out of Heidelberg University. It aimed at understanding and emulating the function and interaction of multiple spatial and temporal scales in brain information processing. Its approach was to combine neurons and synapses in a mixed-signal application using Si transistors. The dual systems created four million neurons and one billion synapses. The TrueNorth [7] chip developed by IBM in Almaden/San Jose CA does not utilize microprocessors but rather intermixes memory with computation. It features custom neural circuits which instantiate one million neuron circuits and 256 million one-bit synapses to demonstrate its own neural model. The claim made by this group is that a synaptic transmission can be executed using only 26pJ. This is a rough indicator of how far away from an ideal implementation the current state of the art is compared to the brain. We are still more than three orders of magnitude away from what may be achievable.

While none of these projects may ultimately become the ideal neuromorphic chip, they perform a very important function by demonstrating proofs of concept. The SpiNNaker Project computer demonstrates configurability that allows different neural models and architectures to be tested. The BrainScaleS Project demonstrated multi-scale functionality and a large density of neurons. The objective was to study the biology of the brain. Unlike SpiNNaker, TrueNorth was designed for commercial application and demonstrated a neuron density of one million while operating at an impressive 70mW. It demonstrated brain-emulating asynchronous event-driven computing rather than using a processor clock. However, unlike the brain, it is an all-digital design, which allowed IBM to exploit the highly automated digital design infrastructure available today. The architecture is non- von Neumann, but the chip is not purely biomimetic.

Continuing on the architecture theme, researchers at MIT [8] have proposed a new architecture for a fully optical neural network that, in principle, could offer an enhancement in computational speed and power efficiency over state-of-the-art electronics for conventional inference tasks. They experimentally demonstrated the essential part of the concept using a programmable nanophotonic processor featuring a cascaded array of 56 programmable Mach-Zehnder interferometers in a silicon photonic integrated circuit, and demonstrated its utility for vowel recognition. As of today, their network still relies on conventional electronics to simulate neuronal firing, but if that step can be implemented optically, then only the training stage will require electronics. Once trained, the network would be able to perform equivalent matrix multiplications two orders of magnitude faster than its fully electronic counterparts. More on optical devices can be found under Section 7 of this chapter.

The most recent attempt at a truly biomimetic device has been provided by the Intel Loihi test chip [9,10,11]. This test chip has self-learning capabilities, which makes it potentially beneficial for autonomous operation and continuous learning in an unstructured environment. Further, it is 1000 times more energy efficient than other ICs which feature trained algorithms, and incorporates many of the features enumerated above. Specifically, it incorporates a fully asynchronous neuromorphic many-core (128) mesh that supports a wide range of sparse, hierarchical and recurrent neural network topologies with each neuron capable of communicating with thousands of other neurons. Each neuromorphic core includes a learning engine that can be programmed to adapt network parameters during operation, supporting supervised, unsupervised, reinforcement and other learning paradigms. It was manufactured using Intel's 14 nm process technology with a total of 130,000 neurons and 130 million synapses. This is six or seven order of magnitude less than what the human brain achieves. As in TrueNorth, the architecture is non-von Neumann and asynchronously timed but the implementation is digital and hence not purely biomimetic.

Recently Intel announced its Pohoiki Springs [25,26] data center, which connects 768 Loihi research chips in a mesh and is making it available to the Intel Neuromorphic Research Community (INRC). Intel claims that it has the

computing power of 100 million spiking neurons. Loihi has inter-chip communication interfaces which allows for a wide range of mesh-based system implementations ranging from two (Kopoho Bay) to 768 (Pohoiki Springs).

To summarize, the ideal solution, if it is to imitate the brain, should demonstrate accuracy at low power with a compact form factor, sparse data representation, local actuation with no central processing, and real time configurability, all leading to a compact, low power learning machine. The most likely path to the ideal is a neural network with massive parallelism, operated in mixed-signal mode at sub-threshold voltages with a non-volatile synapse cell [12] and both cells (neuron and synapse) configurable in real time. Real-time configurability could be achieved via an FPGA approach operating on NVM cells or on simple multiplexers. Massive parallelism could be achieved by using TFTs or van der Waals devices [13], particularly TMCs. The former has the advantage of a volume manufacturing history. The latter has the advantage of theoretically very low sub-threshold slopes and ultra-low leakage, but the disadvantage of never really having been demonstrated in volume production or in the lab with the theoretical values achieved. That is, they are still laboratory devices. Both have the potential advantage of being built in 3D. More discussion on the use of 2D materials can be found in Section 5 of this chapter.

Another promising approach to achieving the desired device characteristics is to use thin tunneling FETs (TFETs) in conjunction with 2D devices [14]. The TFETs do not rely on energy barriers to suppress leakage current, but rather exploit quantum-mechanical tunneling to modulate drain current. Although the band gap of a single-layer 2D crystal semiconductor is well defined, by choosing a suitable heterojunction of dual-doped layers, it is possible to maximize the interlayer tunneling current but maintain a very low sub-threshold slope. The tunneling current can be boosted by the proper choice of heterojunction band offsets between the two 2D crystal layers. This type of tunneling transistor could be the thinnest possible manifestation of a TFET, which can also be scaled to the smallest dimensions, far below what may be feasible with traditional 3D semiconductors. A TFET with a 2D MoS<sub>2</sub> channel contacted with highly doped germanium source electrodes has been reported with a sub-threshold slope of ~32 mV/decade, a supply voltage of <0.1 V and low current values [15]. The goal of achieving such thin TFETs is also forcing controlled growth, doping and heterostructure design, and represent a promising path to achieving the device targets for neuromorphic designs. Further, 1T-FeFET [16] can be used to implement compact synaptic array structures that can be programmed at much lower read/write operating voltages.

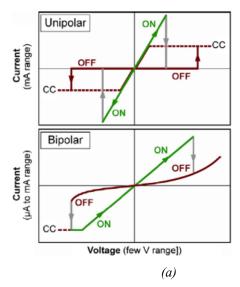

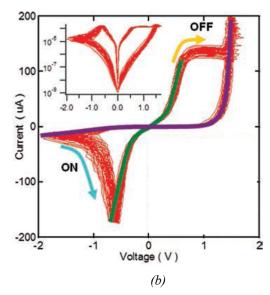

With respect to non-volatility, any of the current bit-readable/writable NVM technologies could be used, but floating and split-gate technologies as well as dielectric storage devices all require comparatively high write voltages. MRAMs and PCRAMs require high write currents. This gives the advantage to memristors [17], SOT [18] MRAMs, STT MRAMs, ReRAMs, FERAMs or CBRAMs. In particular, magneto-metallic spintronic technologies (demonstrating low-threshold switching currents) can be used to implement synaptic crossbar arrays interfaced with neural devices that are potentially an order of magnitude more energy-efficient in comparison to other resistive neuro-mimetic devices [19]. An extended discussion on memristors can be found in Section 5D of this chapter.

Another novel concept exploits one of the characteristics of high-k gate dielectric transistors to create a non-volatile analog-like memory element [20]. Specifically, it is the charge-trapping phenomenon that is leveraged. Experimental data from 22-nm silicon-on-insulator devices reveal that a charge-trap transistor possesses promising characteristics for implementing synapses in neural networks, such as very fine tunability, weight-dependent plasticity, and low power consumption.

Finally, ideas have emerged for building neuromorphic components at the molecular level. With the recent synthesis of cyclocarbon [27], discussions are underway to use this carbon allotrope to design and build elements, which might operate at extremely low power via single electron transfers and perhaps at sub-nanoscale dimensions. To date, no device has been built nor a manufacturing process has been envisioned. Though the potential for achieving brain-like power levels is significant, such technology is still decades away from practical implementation. SIt is nonetheless important to mention because the concept is a research option for developing a truly biomimetic device at extraordinarily low power levels, daunting challenges notwithstanding.

One important issue must be addressed before novel devices can meaningfully impact neuromorphic computing. Although a host of emerging technologies has been envisioned recently, building compact synaptic crossbar-type dense matrices, these devices are generally fraught with several intrinsic inconsistencies including both spatial and temporal variations across multiple devices. How to perform reliable learning with unreliable devices is an important area of research. In references [21-22], new online learning algorithms were developed to demonstrate hardware-friendly learning that overcomes fabrication limitations. It was further shown in ref. [23] that robust learning can be achieved even under various device non-idealities, such as programming non-linearity, spatial and temporal variations, limited resolution in programming, and so on. Such algorithm- and architecture-level innovations are paramount for various emerging nanodevices to make commercial market inroads.

## Technology Gaps and Research needs

The missing pieces are the cells described earlier, an architecture/design that accommodates massive parallelism (>1000 inputs/ neuron), algorithms which control the processing and the models that simulate them, and a method for testing the functionality. In an ideal implementation, the processing is hardwired in the design and defined totally by the inputs. There is no need for a system clock, or PLLs, or a CPU. Harvard and von Neumann architectures and Boolean logic are obsolete. There may be a need for defining a local time window in a cell when signals can be acquired, but that is not known yet. In a wafer-scale HI implementation, some means would have to be provided for controlling the inputs and outputs between chips. Therefore, there would need to be at least one chip with timing and watchdog capability. Once learning algorithms are fully understood, this system timing controller chip could potentially be implemented at the wafer level with a neuromorphic design.

Neuroscientists do not understand in detail how the brain accomplishes the processing it does that results in pattern recognition, cognition, learning and planning. Specifically, signal processing paths have not been worked out, nor the method of steerage. It is not even known whether the steerage is algorithmic. As mentioned previously, how global communication is achieved with no apparent physical link is not understood. This then is the highest priority research need. In the meantime, trial algorithms will need to be tested, which then will require one or many CPUs, and these will require system clocks.

With respect to the devices themselves, research is needed in producing 2D devices in volume, reduction in contact resistance and the ability to incorporate impurity doping into the films. All of the same also applies to heterojunction thin TFETs. This burden can be eased if reliable learning can be achieved with unreliable devices, which then highlights this need as a research objective.

With respect to NVM bits, many of the proposed bits require an electroforming step in order to realize the desired hysteresis characteristics that make them appealing. The results of the electro-formation are highly variable. The need then is to develop a bit that does not require an electroforming step since it would seem that the task of electroforming the billions of bits required is not practical, and even if achieved is likely not to be reproducible. There is some indication by researchers at the University of Texas that a novel 2D memristor structure made of unilayer TMDs might be able to be made into a bit that does not require electroforming and that may be able to switch with an energy approaching the thermodynamic limit (as described in Section 5 of this chapter) and subsequently updated with the use of h-BN [28].

With respect to circuits, spiking neural networks seem to have become the method of choice precisely because they most closely mimic the behavior of neurons. However, most of the large ICs utilizing neuromorphic devices resort to all-digital designs in order to exploit the very mature digital design eco-system. Power reductions have been achieved by migrating away from von Neumann and Harvard architectures while retaining conventional hardware components. But digital circuitry is inherently limited when aspiring to brain-like power levels. As pointed out by Landauer [29], physical processes that are not reversible increase the entropy of a system and when applied to logic gates, operations that are not logically reversible must also increase entropy. From that observation Landauer proffered the principle that the erasure of n bits of known information must always incur a cost of  $nkT \ln(2)$  in thermodynamic entropy. Then, by definition, the thermal energy not available for useful work increases and thus must be dissipated in the system or its surroundings. An inverter is reversible, that is, it can be run backwards in time to retrieve the original condition. An XOR or NAND gate, for example, is not. Thus, substantial reductions in power are in principle achievable if reversible gates were to be developed and used. While there is no physical reason why this could not be done, in the six decades since Landauer's observation no one has succeeded in building a computer using reversible logic, unless one counts quantum computers whose operations are inherently reversible. This is a fundamental limitation and it would seem then that all-digital designs may never be able to achieve brainlike power levels if non-reversible gates are employed.

## **Summary**

The challenges facing HI are formidable. Neuromorphic devices face all of these same challenges but offer a solution to one of the more significant ones, i.e. power consumption. Without a large reduction in power usage, it is difficult to conceive of a practical HI solution that effectively handles many hundreds of amperes of current drawn by a single wafer. On the other hand, neuromorphic devices have their own challenges. To date there have been no demonstrations of a neuromorphic implementation that have come close to the efficiency of the human brain. The state-of-the-art is still three orders of magnitude away. Furthermore, no neuromorphic chip application has found a market niche.

The pivotal issue is that there is an incomplete understanding of the algorithms used by the brain, if indeed its operation is algorithmic at all. Thus, there is not a clear target for chip architecture/design. All the current approaches

use algorithms that require one or more CPUs. This is sufficient for testing the efficacy of various algorithms and neuron and synapse concepts, but is not likely to result in brain-like efficiency. The brain does not use a CPU, at least not the traditional "central" kind.

The ideal implementation will appear when the firmware is wired in the hardware with no system clock and no CPUs. At present, there is no such design; hence progress on the near-term horizon will need to proceed using traditional mixed-signal design methods and components aimed at optimizing algorithms and refining component requirements. The device attributes discussed here anticipate the needs by imitating the various components of the neo-cortex in accordance with our present understanding. Ultimately these attributes will not be "final" until the chip architecture is settled as the optimization is inextricably joined to the device.

#### References

- [1] What Intelligent Machines Need to Learn from the Neocortex, Jeff Hawkins, IEEE Spectrum June 2016, p35ff.

- [2] Purves D, Augustine GJ, Fitzpatrick D, et al., editors. Neuroscience. 2nd edition. Sunderland (MA): Sinauer Associates; 2001. Electrical Potentials across Nerve Cell Membranes.

- [3] Organic core-sheath nanowire artificial synapses with femtojoule energy consumption, Wentao Xu, Sung-Yong Min, Hyunsang Hwang and Tae-Woo Lee, Science Advances 17 Jun 2016: Vol. 2, no. 6, e1501326

- [4] Supercomputers Ready for Use as Discovery Machines for Neuroscience, Moritz Helias, Susanne Kunkel, Gen Masumoto, Jun Igarashi, Jochen Martin Eppler, Shin Ishii, Tomoki Fukai, Abigail Morrison, and Markus Diesmann, Front Neuroinform. 2012; 6: 26.

- [5] The SpiNNaker Project, Steve B. Furber; Francesco Galluppi; Steve Temple; Luis A. Plana, Proceedings of the IEEE (Volume: 102, Issue: 5, May 2014)

- [6] Neuromorphic hardware in the loop: Training a deep spiking network on the BrainScaleS wafer-scale system, Sebastian Schmitt; Johann Klähn; Guillaume Bellec; Andreas Grübl; Maurice Güttler; Andreas Hartel; Stephan Hartmann, Dan Husmann, Kai Husmann, Sebastian Jeltsch, Vitali Karasenko, Mitja Kleider, Christoph Koke, Alexander Kononov, Christian Mauch, Eric Müller, Paul Müller, Johannes Partzsch, Mihai A. Petrovici, Stefan Schiefer, Stefan Scholze, Vasilis Thanasoulis, Bernhard Vogginger, Robert Legenstein, Wolfgang Maass, Christian Mayr, René Schüffny, Johannes Schemmel, Karlheinz Meier, 2017 International Joint Conference on Neural Networks (IJCNN), 2017.

- [7] TrueNorth: Design and Tool Flow of a 65 mW 1 Million Neuron Programmable Neurosynaptic Chip, Filipp Akopyan; Jun Sawada; Andrew Cassidy; Rodrigo Alvarez-Icaza; John Arthur; Paul Merolla; Nabil Imam, Yutaka Nakamura, Pallab Datta, Gi-Joon Nam, Brian Taba, Michael Beakes, Bernard Brezzo, Jente B. Kuang, Rajit Manohar, William P. Risk, Bryan Jackson, Dharmendra S. Modha, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (Volume: 34, Issue: 10, Oct. 2015)

- [8] Deep learning with coherent nanophotonic circuits, Y.Shen, N.Harris, S.Skirlo, M.Prabhu, T.Baehr-Jones, M.Hochberg, X.Sun, S.Zhao, H.Larochelle, D.Englund & M.Soljacic. Nature Photonics, Vol.11, p.441(2017).

- [9] Intel Announces Self-learning AI Chip Loihi, Corinne Reichert, http://www.zdnet.com/article/intel-announces-self-learning-ai-chip-loihi/, Sept 2017.

- [10] https://en.wikichip.org/wiki/intel/loihi

- [11] Loihi: A Neuromorphic Manycore Processor with On-Chip Learning, Mike Davies et al., IEEE Micro (Volume: 38, Issue: 1, January/February 2018)

- [12] A Learning-Enabled Neuron Array IC Based Upon Transistor Channel Models of Biological Phenomena, Stephen Brink; Stephen Nease; Paul Hasler; Shubha Ramakrishnan; Richard Wunderlich; Arindam Basu; Brian Degnan, IEEE Transactions on Biomedical Circuits and Systems (Volume: 7, Issue: 1, Feb. 2013)

- [13] A microprocessor based on a two-dimensional semiconductor, Stefan Wachter, Dmitry K. Polyushkin, Ole Bethge, and Thomas Mueller, Nat Commun. 2017; 8:14948.

- [14] Two-dimensional semiconductors for transistors, Manish Chhowalla, Debdeep Jena and Hua Zhang, 10.1038/natreymats2016.52

- [15] A sub-thermionic tunnel field effect transistor with an atomically thin channel, Sarkar, D. et al. Nature 526, 91–95 (2015).

- [16] 1T Non-Volatile Memory Design Using Sub-10nm Ferroelectric FETs, A. Sharma and K. Roy IEEE Electron Device Letters, vol. 39, no. 3, pp. 359-362, March 2018.

- [17] Integration of nanoscale memristor synapses in neuromorphic computing architectures, Giacomo Indiveri, Bernabé Linares-Barranco, Robert Legenstein, George Deligeorgis and Themistoklis Prodromakis, Nanotechnology, Volume 24, Number 38, Sept 2013.

- [18] Surprises from the Spin Hall Effect, Jairo Sinova and Tomas Jungwirth, Physics Today, July 2017, p.39ff.

- [19] Encoding neural and synaptic functionalities in electron spin: A pathway to efficient neuromorphic computing, Abhronil Sengupta, and Kaushik Roy, Applied Physics Reviews 4, no. 4 (2017): 041105.

- [20] Unsupervised Learning Using Charge-Trap Transistors, Xuefeng Gu, S. S. Iyer, IEEE Electron Device Letters, vol. 38, no. 9, pp. 1204-1207, Sept. 2017.

- [21] N. Zheng and P. Mazumder, "Online Supervised Learning for Hardware-Based Multilayer Spiking Neural Networks Through the Modulation of Weight-Dependent Spike-Timing-Dependent Plasticity," in IEEE Transactions on Neural Networks and Learning Systems, vol. PP, no. 99, pp. 1-16.

- [22] N. Zheng and P. Mazumder, "Hardware-Friendly Actor-Critic Reinforcement Learning Through Modulation of Spiking-Timing Dependent Plasticity," IEEE Transactions on Computers, Vol. 66, No. 2, Feb. 1 2017.

- [23] N. Zheng and P. Mazumder, "Learning in Memristor Crossbar-Based Spiking Neural Networks through Modulation of Weight Dependent Spike-Timing-Dependent Plasticity," in IEEE Transactions on Nanotechnology, to appear.

- [24] Yexin Yan, David Kappel, Felix Neumaerker, Johannes Partzsch, Bernhard Vogginger, Sebastian Hoeppner, Steve Furber, Wolfgang Maass, Robert Legenstein, Christian Mayr, "Efficient Reward-Based Structural Plasticity on a SpiNNaker 2 Prototype," in IEEE Transactions on Biomedical Circuits and Systems. 13 (3): 579–591. arXiv:1903.08500[cs.NE] 2019

- [25] https://newsroom.intel.com/news/intel-scales-neuromorphic-research-system-100-million-neurons/#gs.8i3xgc

- [26] E. Paxon Frady, Garrick Orchard, David Florey, Nabil Imam, Ruokun Liu, JOyesh Mishra, Johathan Tse, Andreas Wild, Friedrich T. Sommer, Mike Davies, "Neuromorphic Nearest-Neighbor Search Using Intel's Pohoiki Springs," arXiv:2004.12691 [cs.NE] 2020.

- [27] Katherine Kaiser, Lorel M. Scriven, Fabian Schulz, Przemyslaw Gawel, Leo Gross, Harry L. Anderson, "An sphybridized Molecular Carbon Allotrope, Cyclo(18)carbon," in Science 20 Sep 2019: Vol.365, Issue 6459, pp1299-1301 DOI:10.1126/science.asy1914.

- [28] Samuel K. Moore, "Atom Thin Switches Could Route 5G and 6G Radio Signals," in IEEE Spectrum. June 1, 2020.

- [29] R. Landauer, "Irreversibility and Heat Generation in the Computing Process," in IBM Journal of Research and Development. 5(3):183-191. Doi:10.1147/rd.53.0183 (July 1961).

## 3. Printed Electronics

This section describes a range of printed devices and challenges related to materials, inks, processes and printing tools. For specific applications related to medical, health and wearable applications and systems, the reader is referred to Chapter 4 of this Roadmap. In addition, 3D printed electronics and additive manufacturing techniques in the context of integrating silicon ICs into systems are covered in Section 10 of Chapter 8.

Using printing techniques for the manufacture of functional electronic devices has the potential to provide a wide range of benefits not easily achieved through conventional processing. Examples include very large area devices, use and integration of an extensive set of functional materials (including polymers, small molecules, nanoparticles, biomaterials, etc.), facile integration with a wide range of substrates (including those that are mechanically flexible/stretchable or contoured), mass customization, ability to rapidly prototype and iterate, as well as low-mass and low-cost devices. Additive manufacturing of electronic systems leads to devices which find applications in many areas such as energy generation and storage, distributed sensing, medical devices, wearable electronics, environmental monitoring systems, information displays, interactive systems, robotics, and transient devices. Moreover, using printing to make electronic systems potentially enables new, distributed, custom manufacturing models that are more inclusive, allowing broader participation in the fabrication of goods with very wide design freedom.

There has been enormous progress in the development of electronic materials for solution-based printing as well as in functional devices and systems made using additive manufacturing techniques. Nevertheless, many multidisciplinary challenges remain for materials, devices and processing in order to achieve the desired potential for printed electronics. For example, as printing relaxes area constraints, some high-performance devices can be readily fabricated such as sensors and electrochemical energy storage devices. However, the typically low-resolution print techniques commonly used now limit our ability to build complex, high performance circuits, due to large feature sizes, low yields, lack of precise control and the electronic properties of solution-processable semiconductors. As such, hybrid approaches are often followed, where printed devices are combined with the pre-fabricated silicon integrated circuits; this adds complexity and reduces design freedom, but enables complex functionality such as high-resolution analog-to-digital conversion and wireless communication. Direct-write print systems that enable resolution of 1 micron or better have been demonstrated, but are typically very slow and not easily parallelized, and may limit the materials set that can be used.

Another example of a significant issue is true process integration for the printing of electronic systems. Complete devices and systems often require some non-print processes such as vacuum deposition or photolithography, as well as removal from the printer for certain steps, such as heating or ancillary chemical treatments. As such, for complex devices, we are generally not able to move from a design directly to a completed system without significant human intervention, thereby limiting the ability of this manufacturing technique and not realizing some potential benefits that printing, particularly digital printing, might provide including layer-by-layer printing for integration with

structural additive manufacturing, and closed-loop feedback for correction or optimization of functional devices. Developing appropriate materials and inks as well as print process and device structures will be key to overcoming these issues. Efforts to produce "all-printed" devices are at their early stage.

## **Printed Electronics for Heterogeneous Integration**

For a baseline, there were essentially three major areas of printed electronics in commercial practice in 2018. First is the oldest usage of polymer thick film conductors principally used for interconnection and things like membrane touch switches. This is complemented by thin film processes that make use of lithography patterning to create everything from thin-film transistors to interconnects. Both approaches converge at touch display and active surface applications that make use of a variety of techniques focused on patterning conductive materials such as Indium Tin Oxide (ITO) or silver, carbon or copper nanowires. The third major area of flexible hybrid electronics is where elements of each of these techniques are blended together with additive processing and packaging methods to integrate silicon ICs into systems (see section 10 of Chapter 8). These combined techniques open a gateway for higher performance integration and more aggressive form factor benefits. As of this writing, the state of the art is the integration of 30 micron pad pitch with conductors either screen printed or aerosol jet printed at a resolution of 20 microns and an aspect ratio of 1:3 with a resistivity of 2.5-3x bulk copper. In the immediate future, there are several areas where we can expect these additive patterning techniques to bring us performance that, while not besting traditional methods on a purely performance standpoint, bring a unique combination of structure, design, materials and temperature that can enable devices not possible today.

Some specific challenges and potential solutions include the following:

## 5-year horizon:

Overcoming the low performance of printed circuits.

Potential solutions:

- Custom, thinned, silicon ICs that provide the correct functionality and integrate readily with printing processes.

- New materials, device types and designs for improved circuit performance.

- Many target applications for printed electronics, such as distributed sensors or wearable electronics, require stand-alone functionality. A reliable printed power source that can harvest energy from the environment and store it on board is needed.

Potential solutions:

- Integration of printed devices that harvest energy from light, heat, motion, etc. with printed energy storage devices such as capacitors or electrochemical cells.

- In-printer layer-by-layer simultaneous printing of multiple device types is currently a challenge due to a variety of off-line patterning and curing steps that are often needed.

Potential solutions:

- Develop materials/inks that can be rapidly cured within the print tool without the need for off-line processing and additional human interaction.

- Integrated print tools that can process a wide range of inks and feature sizes from a single design.

- Simple printed chemical/physical/bio sensors are often not sufficiently selective, thereby limiting their utility.

Potential solutions:

- Develop arrays of similar sensors for improved selectivity; employ machine learning.

- Develop sensor materials and/or membranes for improved selectivity.

- Integration of electronics with 3D structural additive manufacturing would be beneficial, to make complex, complete electromechanical systems.

Potential solutions:

- Integrated print tools, as well as tools designed to print onto curved surfaces.

- Printed electronic skins that can be integrated with 3D structures.

- New print techniques, perhaps with variable voxel size, that are better suited to integration of multiple materials.

- New materials and print techniques to make printed structures compatible with printed electronics.

- Lack of good printed actuators limits ability to make electromechanical systems.

Potential solutions:

- Translate printed electrically-actuated, muscle-like actuators to layer-by-layer print techniques.

- Develop new, print compatible, electrically actuated actuators.

Some specific near-term developments are summarized below:

Replacement of wire bonding – In the near term, printed electronics will be used in its flexible hybrid application to integrate ICs. It is already being used in relatively low-complexity devices to replace traditional electronics, and a great deal of work is underway advancing the reliability, conductivity and printing resolution of these devices. As this work improves and approaches "as deposited and cured" interconnects approaching 2x the bulk resistivity of metallic copper, more and more packaging applications will make use of additive techniques to replace wire bonding or to enable 2.5D integration. This will be especially common in cases where devices such as mixed signal, RF and MEMS elements will be integrated together (see chapters 11 and 12). The gating elements include the resolution, aspect ratio and resistivity of the resultant materials.

Replacement of Solder – A longer term application for printed electronics is to enable integration of devices and systems using conductive adhesives, and plasma or plasma-spray conductors, to replace solder assembly. These approaches will lose the self-centering benefits of solder, but will gain a number of advantages including lower assembly thermal stress as the lower temperature excursion will not create as significant a CTE mismatch. Also, the low-temperature integration (which in some cases can be done at room temperature) enables the integration of non-traditional materials, which are especially interesting in bio applications where certain proteins, biomarkers, or chemicals will not survive a 230°C reflow process. This facilitates the creation of a whole new landscape of biological or chemical sensing devices.

**3D Surface Electronics** – One area where Printed Electronics is supplanting traditional methods is the ability to deposit electronics directly onto curved surfaces. Additive techniques already are replacing lithography-based processes for antenna patterning, and we continue to see use cases where electronics are added to helmets, wing panels, or other elements that either do not have the space or cannot accommodate planar rigid circuit integration. This area continues to see growth, and as the integration of components begins to scale with the printing techniques, more and more niche applications will make use of these processes.

Embedded Electronics for 3D Printing – The vision since the late 1980s has been to integrate 3D printing and printed electronics into a system that can deposit embedded electronics into 3-dimensional parts. There are several hobby platforms that can do this integration in a crude fashion today. However, they are constrained by the layered deposition materials used for the 3D printing. Materials like PLA or ABS filaments or SLA resins do not ensure the best electrical properties. However, there is no intrinsic physics or materials science limitation in this domain. It only remains a matter of multi material deposition, integrated software, and process refinement. These will all be solved via market demands in a 5-year time horizon.