**Chapter 18: Supply Chain**

http://eps.ieee.org/hir

The HIR is devised and intended for technology assessment only and is without regard to any commercial considerations pertaining to individual products or equipment.

We acknowledge with gratitude the use of material and figures in this Roadmap that are excerpted from original sources. Figures & tables should be re-used only with the permission of the original source.

October, 2019 Table of Contents

#### **Table of Contents**

#### To download additional chapters, please visit

#### http://eps.ieee.org/hir

| CHAPTER 1: HETEROGENEOUS INTEGRATION ROADMAP: OVERVIEW |

|--------------------------------------------------------|

| CHAPTER 2: HIGH PERFORMANCE COMPUTING AND DATA CENTERS |

| CHAPTER 3: THE INTERNET OF THINGS (IOT)                |

| CHAPTER 4: MEDICAL, HEALTH & WEARABLES                 |

| CHAPTER 5: AUTOMOTIVE                                  |

| CHAPTER 6: AEROSPACE AND DEFENSE                       |

| CHAPTER 7: MOBILE                                      |

| CHAPTER 8: SINGLE CHIP AND MULTI CHIP INTEGRATION      |

| CHAPTER 9: INTEGRATED PHOTONICS                        |

| CHAPTER 10: INTEGRATED POWER ELECTRONICS               |

| CHAPTER 11: MEMS AND SENSOR INTEGRATION                |

| CHAPTER 12: 5G COMMUNICATIONS                          |

| CHAPTER 13: CO DESIGN FOR HETEROGENEOUS INTEGRATION    |

| CHAPTER 14: MODELING AND SIMULATION                    |

| CHAPTER 15: MATERIALS AND EMERGING RESEARCH MATERIALS  |

| CHAPTER 16: EMERGING RESEARCH DEVICES                  |

| CHAPTER 17: TEST TECHNOLOGY                            |

| CHAPTER 18: SUPPLY CHAIN                               |

| CHAPTER 19: SECURITY                                   |

| CHAPTER 20: THERMAL                                    |

| CHAPTER 21: SIP AND MODULE SYSTEM INTEGRATION          |

| CHAPTER 22: INTERCONNECTS FOR 2D AND 3D ARCHITECTURES  |

| CHAPTER 23: WAFER-LEVEL PACKAGING (WLP)                |

#### **Chapter 18: Supply Chain**

This chapter is in preparation, and will be integrated into the Roadmap at Version 1.1, planned for the end of 2019. In its place is the following summary and a series of slides giving the current status of integrated photonics and some information that is relevant to the progress needed over the next 10 to 15 years.

#### **Executive Summary**

Past technical roadmaps have not addressed supply chain dynamics, as there has not been a need to do so due to a fairly linear ecosystem. However, electronics have shifted away from the monolithic systems that were prevalent in the IT-dominated space, and toward a consumer-focused realm where communications and computing have become pervasive. Inevitably, supply chain dynamics have become far more complex.

With the industry now looking through the applications lens more so than ever, the packaging landscape has undoubtedly been impacted as well. There are several supply chain considerations that come into view as more packaging options become available for various applications. From supply chain trends (e.g., convergence, mergers and acquisitions) to challenges (such as material and equipment capability) to disruptions (e.g., geo-political, natural and human resources, regulatory, environmental health and safety), these factors must be taken into consideration when making technical and business decisions.

**Heterogeneous Integration Roadmap**

### **Chapter 18: Supply Chain**

1

# Outline and Work in Progress

- Background and Objectives

- Scope

- Confined to supply chain dynamics and challenges within heterogeneous integration

- Supply Chain Dynamics

- Map supply chains by package type and application

- Challenges

- Supply chain disruptions and considerations both current and future

- Future Chapter Development

- Connect with supply chain needs and challenges in other HIR working groups

## **Background & Objectives**

- Past technical roadmaps have not addressed supply chain dynamics

- Electronics have shifted from monolithic systems to sense/compute where supply chain dynamics are more complex

- Key Factors

- Product/application complexity

- Geographical and political diversity

- Supply chain disruptions

- Supply chain development

- The focus of this working group will be on awareness as well as guidance on checkpoints for the industry when they are considering specific technical paths.

2

### Scope

- The scope of this group will encompass the full supply chain pertaining to heterogeneous integration (design and manufacturing) with specific focus given to the following:

- 1. Supply chain disruptions and considerations:

- Geo-political ramifications

- Force majeure

- · EHS and regulatory activities

- 2. Supply chain mappings (within scope) and trends:

- Convergence (e.g. front-end equipment now in back-end, PCBA/SMT/EMS starting advanced packaging operations, etc.)

- · M&A, partnerships, and consolidation

- Potential for vertical, horizontal integration (e.g., fabless acquiring fab capabilities)

- Market entrants and exits

# Challenges

- Supply-chain Constraints

- Natural & Human Resources

- Example: Lack of talent availability due to misperceptions around microelectronics

- Geo-political

- Examples: U.S.-China Trade War; Japan-Korea Trade War (materials)

- Regulatory and EHS

- Example: Waste management issues

- Continuity/Resilience

- · Examples: Dual+ sourcing, proximity

- Force majeure

- · Example: Earthquakes, flooding

5

# Challenges (continued)

- Supply-chain Development

- Equipment Capabilities

- Materials Design

- Environmental

- Transactional/Business Models

- Innovation Pipeline

#### Example - "Metal Deposition for Fan-Out Packaging"

- TSV cost forcing shift from one packaging architecture to another

- Emergence of mm-Wave driving need for low loss materials

- · Materials need to be low temperature tolerant, better stress control from compressive to tensile

- PVD systems also need the flexibility to process such materials while maintaining productivity

- The mold and organic dielectrics absorb moisture which must be removed before any plasma processing, otherwise deposited metal will be contaminated

- New chamber designs needed to prevent particle generation (of carbon being a by-product of etch process)

- Chamber temperature control to prevent wafer warpage

- Other considerations for handling increased warpages:

- Vertical clearances in wafer cassettes, robot arm velocities to minimize rapid temperature transitions, optics calibration for wafer handling

- Bond surface contamination of new materials used in FO-WLP negatively affects contact resist leading to reduced battery life (mobile applications). Preclean technology is used to mitigate contaminating gases

7

## Example - "Metal Deposition for Fan-Out Packaging"

| Challenges                                                                                                                                                                                                            | FO-WLP PVD Supply Chain            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| TSV cost forcing shift from one packaging architecture to another                                                                                                                                                     | Trends/Forces                      |

| Emergence of mm-Wave driving need for low loss materials:                                                                                                                                                             | Trends/Forces                      |

| Materials need to be low temperature tolerant, better stress control from compressive to tensile                                                                                                                      | Development – Material Design      |

| PVD systems also need the flexibility to process such materials while maintaining productivity                                                                                                                        | Development – Equipment Capability |

| Mold and organic dielectrics absorb moisture which must be removed before any plasma processing, otherwise deposited metal will be contaminated                                                                       | Development – Material Design      |

| New chamber designs to prevent particle generation (of carbon being a by-product of etch process)                                                                                                                     | Development – Equipment Capability |

| Chamber temperature control to prevent wafer warpage:                                                                                                                                                                 | Trends/Forces                      |

| Other considerations for handling increased warpages —<br>Vertical clearances in wafer cassettes, robot arm velocities to minimize rapid temperature<br>transitions, optics calibration for wafer handling            | Development – Equipment Capability |

| Bond surface contamination of new materials used in FO-WLP negatively affects contact resist<br>leading to reduced battery life (mobile applications). Preclean technology is used to mitigate<br>contaminating gases | Development – Material Design      |

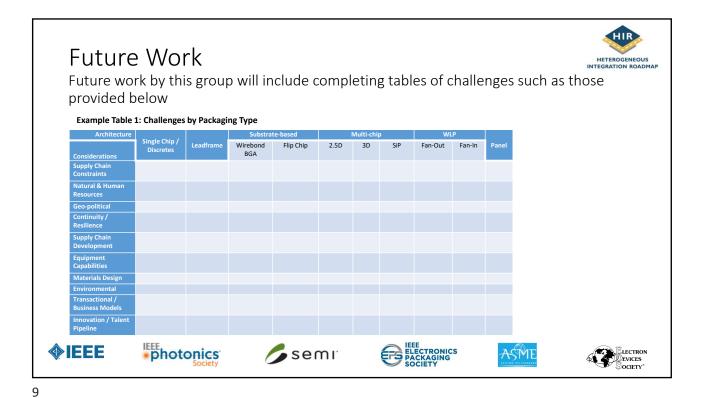

Future Work (continued) HETEROGENEOUS INTEGRATION ROADM **Example Table 2: Challenges by Application** Architecture Other 2.5D Quantum Neuromorphic Considerations Supply Chain Constraints Geo-political Continuity / Resilience Supply Chain Development Materials Design Transactional / Business Models Innovation / Talent

Pipeline \*photonics **�IEEE ∕** semi **ASME**

#### Acknowledgments

## Supply Chain Technical Working Group (TWG)

- John Hunt (ASE US)

- Ming Li (ASM Pacific)

- Tom Gregorich (Carl Zeiss Semiconductor Manufacturing Technology)

- · Rozalia Beica (DuPont)

- Siva Sivasankar (Google)

- · Krish Dharma (IBM)

- Allan Calamoneri

- David Butler (SPTS)

- Paul Trio (SEMI)

- Tom Salmon (SEMI), chair

11