# **2021 Edition**

# **Chapter 8: Single Chip and Multi Chip Integration**

# For updates, visit http://eps.ieee.org/hir

The HIR is devised and intended for technology assessment only and is without regard to any commercial considerations pertaining to individual products or equipment.

We acknowledge with gratitude the use of material and figures in this Roadmap that are excerpted from original sources. Figures and tables should be re-used only with the permission of the original source.

# Table of Contents

| Chapter 1: Heterogeneous Integration Roadmap:<br>Driving Force and Enabling Technology for Systems of the Future |   |

|------------------------------------------------------------------------------------------------------------------|---|

| Chapter 2: High Performance Computing and Data Centers                                                           |   |

| Chapter 3: Heterogeneous Integration for the Internet of Things (IoT)                                            |   |

| Chapter 4: Medical, Health and Wearables                                                                         |   |

| Chapter 5: Automotive                                                                                            |   |

| Chapter 6: Aerospace and Defense                                                                                 |   |

| Chapter 7: Mobile                                                                                                |   |

| Chapter 8: Single Chip and Multi Chip Integration                                                                |   |

| Section 1: Executive Summary and Scope                                                                           | 1 |

| Section 2: Electrical Analysis and System Requirements1                                                          | 0 |

| Section 3: Thermal Management                                                                                    | 8 |

| Section 4: Mechanical Requirements                                                                               | 2 |

| Section 5: Thinning and Singulation                                                                              | 6 |

| Section 6: Wire Bonding                                                                                          | 0 |

| Section 7: Flip Chip and Interconnects                                                                           | 8 |

| Section 8: Substrates4                                                                                           | 2 |

| Section 9: Board Assembly4                                                                                       | 9 |

| Section 10: Additive Manufacturing                                                                               | 3 |

|                                                                                                                  |   |

| Section 11: Electromigration                                                                                     | 7 |

| Section 11: Electromigration                                                                                     |   |

|                                                                                                                  |   |

| Section 12: Summary and Difficult Challenges                                                                     |   |

| Section 12: Summary and Difficult Challenges                                                                     |   |

| Section 12: Summary and Difficult Challenges                                                                     |   |

| Section 12: Summary and Difficult Challenges                                                                     |   |

| Section 12: Summary and Difficult Challenges                                                                     |   |

| Section 12: Summary and Difficult Challenges                                                                     |   |

| Section 12: Summary and Difficult Challenges                                                                     |   |

| Section 12: Summary and Difficult Challenges                                                                     |   |

| Section 12: Summary and Difficult Challenges                                                                     |   |

| Section 12: Summary and Difficult Challenges                                                                     |   |

| Section 12: Summary and Difficult Challenges                                                                     |   |

| Section 12: Summary and Difficult Challenges                                                                     |   |

| Section 12: Summary and Difficult Challenges                                                                     |   |

| Section 12: Summary and Difficult Challenges                                                                     |   |

# **Chapter 8: Single Chip and Multi Chip Integration**

# Section 1: Executive Summary and Scope

# 1. 2020 – 2021 Disruptions, Dislocations and Innovations

History will mark the years 2020 and 2021 as a period of rapid global disruptions, dislocations and global innovations on a scale seldom seen in history in peacetime. Disruptions included COVID-19, extreme wild fires, and flooding across the globe, accompanied by climate change and semiconductor shortages.

Send corrections, comments and suggested updates to the TWG chair, using our HIR SmartSheet:

https://rebrand.ly/HIR-feedback

In January 2020, the HIR team and the EPS Santa Clara Valley Chapter, together with SEMI colleagues, were planning the 3rd HIR symposium and annual meeting, February 23-24, with all the excitement towards celebrating the release of the 1st HIR edition in October 2019. We moved the annual meeting site from the new Samsung showcase facility in San Jose to SEMI's Global Headquarters in Milpitas when the Samsung site was closed to visitors. This meeting was hugely successful, with much networking in formalized work sessions, during luncheons and a wine tasting event, and business card exchanges. The day after this HIR conference, some of our industry colleagues started to receive notices from their companies restricting conference travel attendance to mitigate COVID-19 risk.

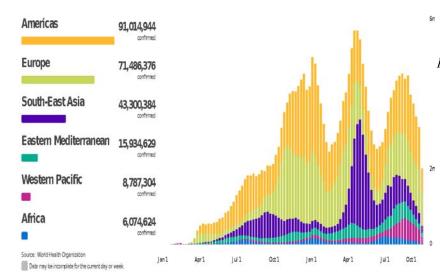

Little did we imagine the extent and ravages of the COVID-19 pandemic that we know today. Shown below are data from the dashboard of World Health Organization October 6, 2021.

Figure 1A: Globally, as of 6pm CEST, 8 October 2021, there have been 236,599,025 confirmed cases of COVID-19, including 4,831,486 deaths, reported to WHO. As of 6 October 2021, a total of 6,262,445,422 vaccine doses have been administered.

Figure 1B: Regional distribution of confirmed cases of Covid 19 Globally, as of 8 October 2021, reported to WHO. (Source: WHO dashboard)

How do electronics and semiconductors contribute to fighting the COVID-19 pandemic crisis? Medical workers in hospital ICUs and emergency rooms depend upon medical equipment/devices powered by highly sophisticated electronics for diagnostics, monitoring and patient care. Good examples are portable semiconductor ultrasonic devices for patient lung imaging diagnostics, and life-saving ventilators for automated oxygen level monitoring and oxygen delivery when patients contract the COVID-19 virus.

The pandemic generated huge amounts of data in different data formats that researchers use for vaccine development, biometrics, etc, in different formats and languages. Cutting-edge computing capabilities for rapid response and accelerated development, data searching, discovery, and analysis were provided. One such effort is the COVID-19 HPC Consortium spearheaded by the U.S. White House, Department of Energy, national laboratories and industry. (Source link: covid19-hpc-consortium.org)

As the WHO recorded 6,262,445,422 vaccine doses administered, it is worth noting that the accelerated vaccine development went from laboratory to manufacturing and distribution to the population in a short period of days, weeks, and months thanks to many dedicated people in the knowledge supply chain and public health institutions. An article titled "The Tangled History of mRNA Vaccine" in Nature (Volume 597 page 318, September 16, 2021) by Elie Dolgin noted that hundreds of scientists have toiled to advance and to expand the science knowledge base in mRNA to realize its health potential. Not until the COVID-19 pandemic were there calls to urgent action for collaboration and sources of funding leading to breakthroughs in vaccine design, development and trial globally." In commercial product terms, product volume drives innovation, operational learning and business – true for the vaccine and true for semiconductors and electronics.

Throughout the many months of pandemic-driven lock-down, the IT infrastructure (semiconductor, packaging and electronics system-based) has been highly robust in maintaining communication between businesses and customers, colleagues and families, teachers and students, in remote working, shopping, and virtual everything. The pandemic has accelerated the transformation to the digital economy while keeping global commence spinning. Hospitals can order goods online, and stay connected. Critically, scientists could develop treatments and vaccines to begin making the world healthy again. Without semiconductors and the resultant products and services, and using the world's most advanced supercomputers, for example, the historically rapid development of COVID-19 vaccines would not have been possible.

In June 2021, the White House issued a report titled "Building Resilient Supply Chains, Revitalizing American Manufacturing, and Fostering Broad-Based Growth". This report is in response to the Presidential Executive Order 14017 issued in February 2021, "America Supply Chains", directing the administration to perform a 100-day review, due June 2021, to assess supply chain vulnerabilities across four key product areas. They are:

- Semiconductor Manufacturing and Advanced Packaging

- Large Capacity Batteries

- Critical Materials

- Pharmaceutical and Active Pharmaceutical Ingredients

Figure 2: Cover page of White House Report "Building Resilient Supply

Chains Revitalizing American Manufacturing, and Fostering Broad-Based Growth". June 4 2021 BUILDING RESILIENT SUPPLY CHAINS, REVITALIZING AMERICAN MANUFACTURING, AND FOSTERING BROAD-BASED GROWTH

100-Day Reviews under Executive Order 14017

June 2021

A Report by The White House

The report begins with:

"The COVID-19 pandemic and resulting economic dislocation revealed long-standing vulnerabilities in our supply chains. The pandemic's drastic impacts on demand patterns for a range of medical products including essential medicines wreaked havoc on the U.S. healthcare system. As the world shifted to work and learn from home, it created a global semiconductor chip shortage impacting automotive, industrial, and communications products, among others."

1

The US Government and Congress has legislation underway to invest US\$52 billion on semiconductor and advanced packaging research. Companies including Intel, TSMC, Samsung and Texas Instruments have announced plans to invest many billions in wafer fab manufacturing capacity expansion.

Going forward, we are expecting expanding advances of electronics markets and applications in Internet of Things, Mobile Devices and Network Infrastructure, Automotive, Aerospace and Defense, and of course Medical, Health and Wearables technologies and products. They will be connected by 5G communications and further empowered by AI and ML.

# These Six Markets & Applications will be further transformed through the power of AI

Figure 3: Six Major Markets and Applications

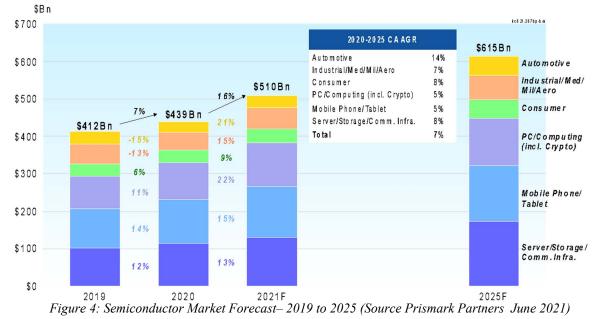

Shown above is the Semiconductor market size forecast for different market applications in Figure 3 from 2019 to 2025.

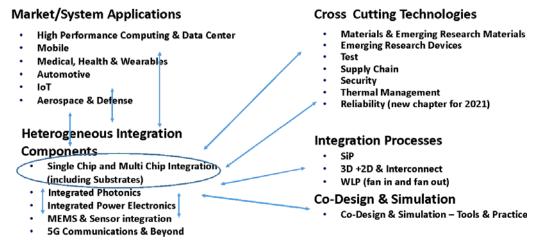

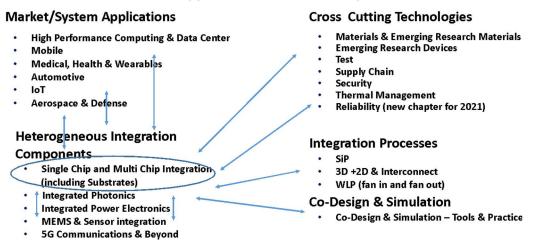

# 2. Heterogeneous Integration Roadmap

The Heterogeneous Integration Roadmap comprehensively covers the entire semiconductor and electronics technology ecosystem (see Figure 5). It serves as the knowledge-based roadmap for future electronics technology. The Roadmap is market- and application-driven, starting with six specific market segments: High Performance Computing and Data Center, IoT, 5G Communications and Beyond, Smart Mobile, Automotive, Wearable and Health, and Aerospace and Defense. They are followed by 5 Heterogeneous Integration Components, 7 Cross Cutting Technologies, 3 Integration Processes areas, and last but not least, Co-Design and Simulation. Each Technical Working Group contributes a chapter of the Roadmap. Together they work in collaboration to produce this roadmap. We represent the total technology ecosystem – industry, academia, and the research community.

# Heterogeneous Integration Roadmap

An Application Driven Roadmap

Figure 5: Heterogeneous Integration Roadmap structure

This Single and Multichip Integration Chapter covers the basic knowledge, base tools and physical manufacturing infrastructure tools across all market segments. This chapter serves as the packaging "tool box" to the other HIR technical working groups for roadmap readers. The eleven sections form the key technology building blocks from manufacturing processes and physical infrastructure to packaging knowledge base and data.

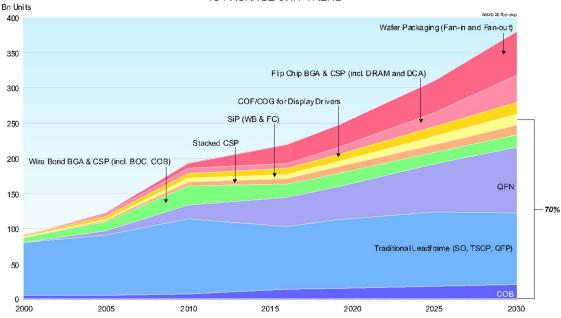

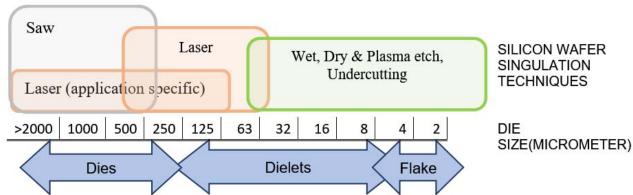

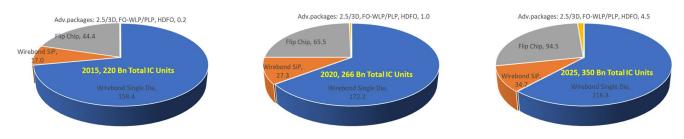

IC devices start as wafers from foundries, thinned and singulated into "chips". While wirebond remains the interconnect workhorse of the industry, there is very strong growth in Flip Chip (BGA-CSP) and WLCSP, wafer-level packaging (fan-In and fanout) and a rapid growth rate for advanced packages as shown in Figure 6.

IC PACKAGE UNIT TREND

Figure 6: Chip-package interconnect technology trends (Bn units) (Source: Prismark Partners 06-2021)

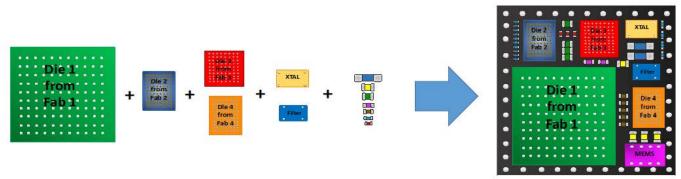

The ICs are assembled and packaged on substrates into components and the components are mounted on boards. Additive manufacturing is emerging that may see implementation across all the interconnect and assembly processes. In architecture and design of components, and systems, architects and design engineers consider electrical, thermal, and mechanical performance requirements, and addresses quality and reliability issues such as electromigration. Together, the following eleven sections form the knowledge and manufacturing infrastructure in the implementation for Heterogeneous Integration for electronics products. Following Moore's words, our purpose in Heterogeneous Integration is to build large systems out of smaller functions, including System in Package (SiP) and Chiplets – which are separately designed, packaged, interconnected, qualified, manufactured and sold.

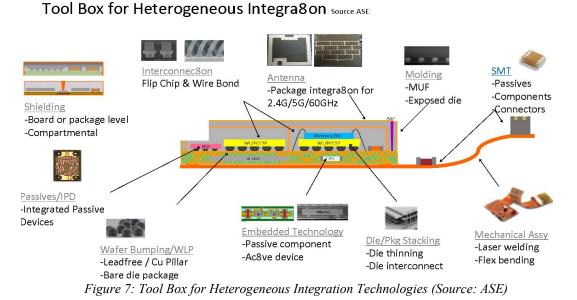

A basic set of tool box for SiP and Heterogeneous Integration is illustrated in Figure below. This well established design and manufacturing ecosystem has been highly productive, flexible, and responsive in producing electronic products across the whole spectrum of products serving consumers and industries large and small, well-established companies and new startups building SiPs and through heterogeneous integration from Home Assistants, Smart Phones, Data Centers, Automotives, Avionics, and many other products in the trillion dollars global electronics market.

Our purpose in Heterogeneous Integration is to build large systems – System in Package – out of smaller functions which are separately designed, packaged, interconnected and manufactured. The twelve sections in this chapter articulate the basic tool sets – infrastructure and knowledge – for heterogeneous integration for all the market segments.

Figure 8: Heterogeneous Integration and System in Package (SiP) (Source ASE)

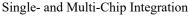

The smartphone industry has been an effective adopter of Heterogeneous Integration Technology in the use of SiP for its advantage in miniaturization, with its modularity allowing product rollout to subsequent generations in the market place. The application processor, housed in a PoP package with the memory component stacked in close proximity on the top, is almost always of the most advanced node. They are the premier examples of SiP, incorporating the most advanced-node processor integrated with a memory die in close proximity, for the demanding consumer market.

# Rear PCB Inside

- A. Apple A15 Applications Processor

- B. Flash Memory

- C. Qualcomm SDX60M 2G-5G Baseband

- D. Qualcomm SDR868 2G-5G TRx (sub-6GHz)

- E. Qualcomm SMR526 5G IF TRx (mmWave)

- F. Power Manger (Apple, Qualcomm, TI, ST, etc)

- G. Apple/Cirrus Logic Audio Amplifier

© Prismark Partners LLC

- H. Apple/Cirrus Logic Audio Codec

- I. FEM (Broadcom, Murata, Skyworks, etc)

- J. USI WiFi Module

- K. USI UWB Module

- L. Broadcom Wireless Charging

- M. NXP Display Manager

- N. 5G mmWave Module

- O. NXP NFC Controller

Figure 9: Apple iPhone 13 Pro main board assembly (Source Prismark Partners)

Shown above is the main board of the iPhone 13 Pro. The main processor die is housed in a PoP package, flipchip assembled on an advanced substrate together with a wirebonded memory component on top. There are multiple modules, including 2G-5G Baseband, 2G-5G TRx (sub-6GHz and mmWave), multiple power managers from different sources, logic, audio amplifier, logic audio codec, FE modules, WiFi modules, UWB modules, wireless charging, Display manager, 5G mmWave module, and NFC controller. They are tightly assembled with many passives on a rigid-flex board. To paraphrase Dr Moore, availability of large functions in the form of SiPs, combined with functional design and construction, should allow the manufacturer of large systems (eg, a smartphone) to design and construct models from one product generation to another, both rapidly and economically, for the hugely competitive consumer market.

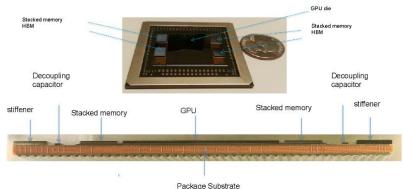

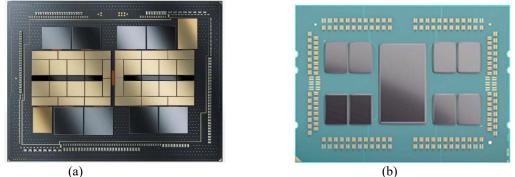

Let us now consider the High Performance Computing and Data Center market application. Shown in Figure 10 is an example of Heterogeneous Integration through SiP, with integration of the processor and HBM memory stack on a silicon interposer platform. The package provides massively parallel high-bandwidth connectivity to the HBM, significant power savings, and greater than 50% shrinkage in X-Y form factor.

Figure 10: AMD Fiji GPU – HDM on Si Interposer 2.5 D Package (Source ASE)

The silicon interposer is a physical substrate platform for the CHIPS program, a part of the DARPA Electronics Resurgence Initiative. CHIPS stands for Common Heterogeneous Integration and Intellectual Property IP Reuse Strategies Program. The vision is an ecosystem of discrete, modular IP blocks, to be assembled into a system using existing and emerging integration technologies.

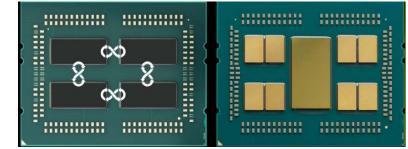

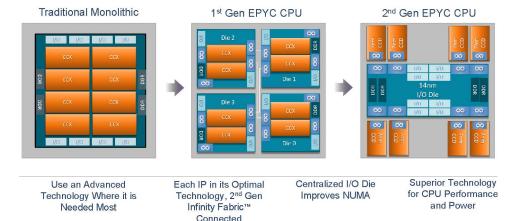

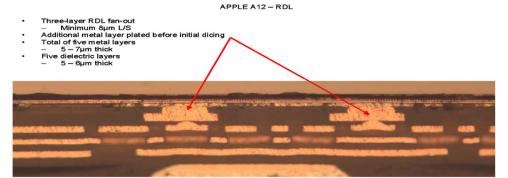

At the advanced nodes, the die yield falls exponentially with die size. Splitting a large monolithic SoC into smaller, tightly coupled die, first demonstrated by Xilinx on a silicon interposer, are now being seriously considered and executed. At the same time, die cost per unit area is escalating [2]. Shown below are two generations of the AMD EPYC server processors. To the left, the large monolithic SoC has been split into four tightly coupled die (for better yield) called chiplets, in homogeneous integration on an organic substrate. To the right there are two groups of four 7-nm chiplets on each side of the larger 14 nm I/O die in heterogeneous integration to optimize unit area die cost.

Figure 11 A: Examples of System Integration – 1st and 2nd Generations EYPC Server Processors (Source AMD)

Figure 11 B: Chiplets in Heterogeneous Integration - EYPC Server Processors (Source AMD)

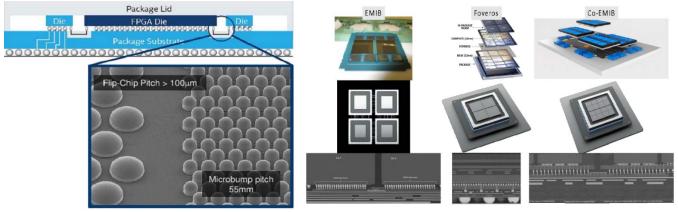

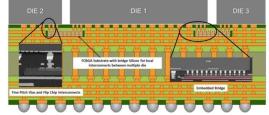

The emergence and growth of chiplet technology, as shown in Figure 11A and 11B, is transitioning the industry into the post-Moore semiconductor era. Using chiplets is the game-changer in this new era for dis-aggregation of monolithic SOCs for economics, time to market, and integration advantages. Components of different nodes or from different companies may be heterogeneously integrated together in one SiP, such as implemented in Intel's Kaby Lake G card, which incorporates a CPU with an AMD GPU linked to 4GB of HBM2. Silicon bridge on organic substrate (EMIB) developed by Intel was used to link multiple die together in close proximity in the package [3].

*Figure 12A: Silicon bridge on substrate technology (EMIB) from Intel for Heterogeneous Integration. Figure 1.12B: Advance Package Chiplet Integration Technologies at Intel: EMIB, Foveros and Co-EMIB (Source Intel)*

Extending the EMIB technology, Foveros and Co-EMIB designs form the advanced technology family in Intel to link multiple die (chiplets) on substrates in the package, as shown in Figure 12B.

Figure 13: Wafer Level Fan-Out integrating 14 nm and 22 nm die in multichip package (Source ASE)

Wafer Level Fan-Out technology was initially developed for addressing the WLCSP form factor for BGA balls. The same manufacturing infrastructure has been utilized to integrate two die from dissimilar nodes into one multidie package shown in Figure 13.

The previous examples demonstrate the growing momentum for SiP and chiplets in high-performance computing – taking a new look at system architecture and expanding innovations in our packaging tool box. We are now seeing the "chiplet initiative" utilizing different packaging technologies for disparate system applications. As the industry goes further into single-digit nodes, considerations of cost, time to market, high bandwidth, and performance per watt make multi-die (SIP and chiplets) heterogeneous integration an important trend going forward [4-10].

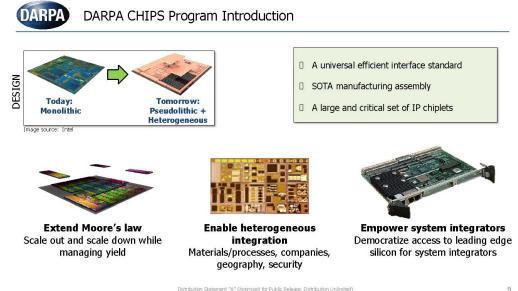

Figure 14: Chiplets in DARPA CHIPS Program: (Source DARPA)

At SEMICON West, July 2019, Andreas Olofsson, DARPA Microelectronics Technology, presented a talk illustrating chiplets in the DARPA CHIPS program. Using the chiplets concept, the program is aimed at three goals (Figure 14): (a) extending Moore's Law; (b) enabling heterogeneous integration; and (c) empowering system integrators.

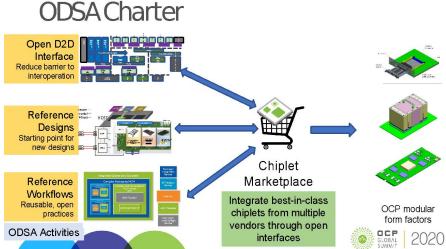

Figure 15: Chiplets in Commercial Perspective (Source: OCP – ODSA)

At the OCP Summit in May 2020 and HIR Workshop in February 2020, Bapi Vinnakota presented the charter for ODSA, which projects a commercial perspective vision of chiplets, with a commercial chiplets marketplace, enabling integration of best-in-class chiplets from multiple sources with heterogeneous integration for commercial electronics products (see Figure 15).

The scope of this Single Chip and Multichip chapter is designed to articulate the current state of the art of two fundamental tool boxes:

- (a) Knowledge Base and Data for Package and System Architecture and Co-Design

- (b) Package Assembly Manufacturing Flow for Substrates and Boards

We ask the questions: *What is the status of leading edge technologies in our tool box for SiP, chiplets and Heterogeneous Integration? What are the challenges ahead? What are the potential solutions?* We shall address these questions, and include in the roadmap the electrical, thermal and mechanical technology issues from device packaging to subsystem and system packaging, from system-package-device architecture and co-design to manufacturing, inclusive of the total ecosystem. Following Moore's words, our purpose in Heterogeneous Integration is to build large systems out of smaller functions – chiplets, SiP modules, and other functional packages – which are separately designed, packaged, interconnected and manufactured. This is the purpose and theme of the Roadmap. This Chapter starts with a section on Scope followed by 11 sections on key technology building blocks from Knowledge Base and Data to Manufacturing and Physical Infrastructure.

- Knowledge Base and Data for Package and System Architecture and Co-Design

- Electrical Analysis and System Requirements

- Thermal Management

- Mechanical Analysis

- Electromigration

- Reliability

- Package Assembly Manufacturing Flow Substrates and Boards

- Wafer Singulation and Thinning

- Wirebond

- Flip Chip

- Substrate

- Board Assembly

- Additive Manufacturing

The Knowledge Base and Data and Manufacturing and Physical Infrastructure form the base foundation for Advanced Packaging and Integration technologies from 2D, 2.5D and 3D, for SiP and wafer level packaging. This chapter links to the other chapters in the Roadmap. Working together with other TWGs, we describe the current state of the art, and the roadblocks in the path going forward, to stimulate pre-competitive research and innovation as much as 15 years ahead.

### 1.7. References

- 1. "Cramming More Components onto Integrated Circuits" Gordon Moore, pp 114 117 Electronics April 19, 1965

- 2. Keynote Presentation by Lisa Su, SEMICON West, July 9, 2019.

- 3. Presentation by R. Mahajan at SEMI 3D Summit January 2019.

- 4. "Making Chip Packaging Simpler" Ed Sperling & Mark Lapedus, Semiconductor Engineering, March 21, 2019.

- 5. "Intel's View of Chiplet Revolution" Samuel Moore, IEEE Spectrum, April 12, 2019

- 6. "Turn to Chiplets" Tom Simonite, Wire, November 6, 2018

- 7. "Modular Routing Design for Chiplet-based System" Jieming Yin et al, ACM/IEEE 45th International Symposium on Computewre Architecture, 2018 pp 726-738.

- 8. Open Domain-Specific Architecture Workgroup Working Paper Draft v0.9 2018 titled "Open Domain-Sp;ecific Architecture A chiplet based open architecture"

- 9. "Waiting for Chiplet Interfaces", Brian Bailey, Semiconductor Engineering, June 13, 2019

- 10. Momentum Gains for an Open-Chiplet Ecosystem" Dylan Mcgrath, EE Times June 18, 2019

# Acknowledgments

The Single and Multichip Integration TWG has over 35 volunteer contributors from industry and academia. We are very fortunate to have this very knowledgeable team making our chapter a reality for our profession and our industry.

| <u>I WG Ch</u> | air William Chen and Co-Chair Anne    | <u>ette l'eng</u>                                     |

|----------------|---------------------------------------|-------------------------------------------------------|

| Section 1      | Background and Scope                  | Bill Chen (ASE)                                       |

| Section 2      | Electrical Requirements               | Lei Shan (Tekollect)                                  |

| Section 3      | Thermal Management                    | Bahgat Sammakia, Scott Schiffres, Srikanth Rangarajan |

|                |                                       | (BU)                                                  |

| Section 4      | Mechanical Requirements               | Benson Chan (BU)                                      |

| Section 5      | Wafer Singulation & Thinning          | Annette Teng (Promex)                                 |

| Section 6      | Wire Bond                             | Ivy Qin (KnS)                                         |

| Section 7      | FlipChip                              | Mark Gerber (ASE)                                     |

| Section 8      | Substrate                             | Kyu-Oh Lee (Intel)                                    |

| Section 9      | Board Assembly                        | Jim Wilcox (UIC)                                      |

| Section 10     | Additive Manufacturing                | Kris Erickson (Facebook), Dishit Parekh (Intel)       |

| Section 11     | Electromigration                      | Paul Ho (UT), Valeriy Sukharev (Mentor)               |

|                |                                       | Eric Cotts (BU), Faramarz Hadian (BU)                 |

| Section 12     | Summary & Difficult Challenges        | Bill Chen                                             |

|                | · · · · · · · · · · · · · · · · · · · |                                                       |

TWG Chair William Chen and Co-Chair Annette Teng

We are pleased to announce that the Reliability Section from previous Roadmap editions has been spun off to form a separate Technical Working Group as Chapter 24 of the Roadmap. Our best wishes to the new Reliability TWG team of Abhijit Dasgupta (UMD), Richard Rao (Marvell) and Shubhada Shasrabudhe (Intel).

# Section 2: Electrical Analysis and System Requirements

# 2.1 Introduction

As system integration migrates from "on-chip" to "in-package", I/O signal integrity (SI) and package-level power distribution effectiveness (PI) become essential to sustaining system advancement. The scale of integration varies from application to application, and so do the SI and PI requirements. In this section, three representative applications are selected for the context of electrical analysis, i.e. Memory, Mobile, and High Performance. In general, "Memory" drives the demands of integration density and bandwidth, "Mobile" drives miniaturization and power reduction, and "High Performance" drives the limits of I/O bandwidth as well as integration technologies.

#### Table 1: Single- and Multi-Chip Integration Technology Requirements

| Year of Production                                 | 2021      | 2022      | 2023      | 2024      | 2025      | 2026      | 2027      |

|----------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| On-chip feature size (nm)                          |           |           |           |           |           |           |           |

| Memory (DDR/HBM)                                   | 10        | 7         | 7         | 5         | 5         | 3         | 3         |

| Smart Phone / Laptop                               | 5         | 5         | 3         | 3         | 2         | 2         | 2         |

| High-performance (notel), chiplet/monolithic       | 7         | 5         | 5         | 3         | 3         | 2         | 2         |

| Maximum Average Power Density (W/mm <sup>2</sup> ) |           |           |           |           |           |           |           |

| Memory (DDR/HBM) (note2)                           | 0.06/0.12 | 0.05/0.11 | 0.05/0.11 | 0.04/0.1  | 0.04/0.09 | 0.04/0.08 | 0.04/0.07 |

| Smart Phone / Laptop                               | 0.5       | 0.5       | 0.55      | 0.55      | 0.6       | 0.6       | 0.65      |

| High-performance                                   | 0.9       | 0.95      | 0.95      | 1         | 1         | 1.05      | 1.05      |

| Core Voltage (Minimum Volts)                       |           |           |           |           |           |           |           |

| Memory (DDR/HBM)                                   | 1.2       | 1.1       | 1.1       | 1         | 1         | 0.9       | 0.9       |

| Smart Phone / Laptop                               | 0.75      | 0.75      | 0.75      | 0.75      | 0.7       | 0.7       | 0.7       |

| High-performance                                   | 0.8       | 0.75      | 0.75      | 0.75      | 0.75      | 0.7       | 0.7       |

| Package Pin count Maximum                          |           |           |           |           |           |           |           |

| Memory (DDR/HBM)                                   | 288/3200  | 288/3200  | 288/3200  | 326/4100  | 326/4100  | 350/4700  | 350/4700  |

| Smart Phone / Laptop                               | 1212/7000 | 1212/7000 | 1275/7600 | 1275/7600 | 1396/8400 | 1396/8400 | 1396/8400 |

| High performance (note3)                           | 6400      | 7800      | 7800      | 9600      | 9600      | 11200     | 11200     |

| Minimum Package Dimension (mm)                     |           |           |           |           |           |           |           |

| Memory (DDR/HBM)                                   | 133       | 133       | 133       | 133       | 133       | 133       | 133       |

| Smart Phone / Laptop                               | 50        | 50        | 55        | 55        | 60        | 60        | 60        |

| High-performance                                   | 79        | 87        | 87        | 95        | 95        | 103       | 103       |

| Performance: On-Chip                               |           |           |           |           |           |           |           |

| Memory (DDR/HBM), MHz                              | 800       | 800       | 1000      | 1000      | 1200      | 1200      | 1600      |

| Smart Phone / Laptop, GHz                          | 3.2       | 3.2       | 4         | 4         | 4.8       | 4.8       | 5.2       |

| High-performance, GHz                              | 6.4       | 8         | 8         | 9.6       | 9.6       | 11.2      | 11.2      |

| Interconnect: Chip-to-Chip (note4)                 |           |           |           |           |           |           |           |

| Memory (DDR/HBM), Gb/s                             | 3.2/2.0   | 4.8/4.0   | 5.2/4.0   | 6.4/4.0   | 6.4/4.0   | 7.8/6.4   | 8.0/6.4   |

| Smart Phone / Laptop, Gb/s                         | 50        | 100       | 100       | 100       | 200       | 200       | 200       |

| High-performance, Gb/s                             | 32        | 32        | 56        | 56        | 64        | 64        | 112       |

| Interconnect: Pkg-to-Board                         |           |           |           |           |           |           |           |

| Memory (DDR/HBM), Gb/s                             | 6.4/3.2   | 8/6.4     | 8/6.4     | 9.6       | 12.8      | 16        | 25        |

| Smart Phone / Laptop, Gb/s                         | 50        | 100       | 100       | 100       | 200       | 200       | 200       |

| High-performance, Gb/s                             | 32        | 56        | 56        | 64        | 64        | 112       | 112       |

Table 1 is a brief summary of the metrics relevant to system requirements – particularly signal and power integrity for various application scenarios – as well as the technology trends evolving from current to foreseeable future (6 years). In summary, the demand of power reduction continuously drives lower voltage and leakage current (on-chip feature size). Meanwhile, power density in high-performance applications tends to grow with emerging 3D and 2.xD packaging technologies. Particularly, both artificial intelligence and accelerator architectures involve heterogeneous devices/components, which further drives the increase in package pin count as well as dimensions.

In the heterogeneous multi-chip packaging environment, input/output interconnections play an important role in system performance. In addition to data bandwidth and signal integrity, common I/O standards are desirable for the ease of complex system designs with devices/components from various sources. In late 2019, The Open Compute Project (OCP) announced significant progress through the Open Domain-Specific Architecture (ODSA) subproject in the development of a chiplet-based architecture. The ODSA subproject's mission is to define an open interface and architecture that enables the mixing and matching of silicon chiplets from different vendors. To achieve this goal, multiple working groups within the ODSA have been established: The ODSA PHY interface group is tasked with defining a simple, open, flexible data-rate interface between chiplets, by defining a new low-power Bunch of Wires (BoW) interface for low-cost packaging technologies; The ODSA Proof of Concept (PoC) group is tasked with validating the technology proposals from the program; The ODSA Business Working Group is tasked with defining HIR 2021 version (eps.ieee.org/hir) Chapter 8, Page 11 Heterogeneous Integration Roadmap

a workflow and business processes to enable companies to assemble products from the marketplace. More interconnect options and specifications are to be detailed in the following sections.

# 1. Chiplet Trend

With the continuous decrease in on-chip feature size, high-end semiconductor manufacturing cost increases exponentially with chip dimensions due to significant yield impact, and therefore, instead of continuously growing, integrated circuits will be divided into "chiplets" with respect to functional regions to take full advantages of semiconductor technologies for the yield optimization and rely on package-level integration to deliver the most cost-effective system performance.

What makes chiplet design different from other SoC design methodologies that have existed for many years is that many of these new chiplet-based parts are putting together pieces that are made on different process technologies. So, for example, a chiplet design might link a 5 or 7 nm CPU with a 10 nm or 14nm I/O element over high-bandwidth die-to-die interconnect. The reason for making these kinds of changes gets to the very heart of some of the transformational developments now impacting the semiconductor business. First, as has been widely discussed, traditional Moore's Law advances in shrinking transistor size have slowed down tremendously, making it difficult (and very expensive) to move all the elements inside a monolithic chip design down to smaller process geometries. Plus, even more importantly, it turns out that some important elements in today's chip designs, such as analog-based I/O and some memory technologies, actually perform worse (or simply the same, but at a significantly higher cost) in smaller feature-sized chips. Therefore, some semiconductor components are better off staying at larger technology nodes. In addition, the processing requirements for different types of workloads (such as AI acceleration) are expanding, leading to the need to combine even more types of processing technology onto a single component. Finally, there have been some important advances in chip packaging and interconnect technologies that are making the process of building these multi-part chiplets more efficient.

In order to efficiently deliver power and data to these various chiplets, leading semiconductor companies have been working on advancing their packaging technologies for the last several years. For instance, Intel announced some important new additions to its arsenal of chip packaging capabilities at Semicon West 2020, all designed to enable even more sophisticated, more flexible, and better yielding chiplet-based products in the years to come. They logically combine EMIB and Foveros, so called "Co-EMIB", that enables both 2D-horizontal and 3D-vertical connections of components in a single package. They also developed a technology called ODI (Omni-Directional Interconnect), which works through and across chips to provide the low-power and low-latency connections needed to attain performance closer to monolithic chip designs, together with a new version of their AIB (Advanced Interface Bus) standard called MDIO that provides the physical layer connect for die-to-die connections used in EMIB.

On the other hand, AMD has been successfully implementing the chiplets concept into their EPYC-family product for years, by leveraging existing organic build-up substrate technology and off-the-shelf die-to-die interconnect IPs. Though this represents a significant divergence from traditional semiconductor advances, it's become abundantly clear that the future of the semiconductor industry is going to be driven by chiplets. With more and more similar implementations, there's no question that the flexibility that chiplets enable is going to be critically important for advances in semiconductors and computing overall. As a result, heterogeneous packaging solutions will dictate chip and system architectures, and become essential to the advancement of the semiconductor industry.

# 2. On-package interconnections

As the semiconductor industry continuously scales down feature size, costs for yielding large dies increase significantly. Compared to 250 mm<sup>2</sup> die on the 45 nm process, the 16 nm process more than doubles the cost/mm<sup>2</sup> and the 7 nm process nearly doubles that to 4x the cost per yielded mm<sup>2</sup>. Moving to the 5 nm and even 3 nm nodes, the cost is expected to continue to increase. Fabricating large monolithic dies will becomes increasingly less economical. As one solution to easing the economics of manufacturing chips with a large amount of transistors, the industry has started shifting to chiplet-based design whereby a single chip is broken down into multiple smaller chiplets that are "re-assembled" at the package level, which demands significant interconnect bandwidth. In addition, other heterogeneous components, such as HBM, GPU, and FPGA, are then integrated in the package simultaneously. The scale and complexity of SiPs requires greater carrier dimensions as well as higher interconnect density, which in turn drives the development of innovative packaging solutions.

In addition, to take full advantage of multi-chip packaging, it is critical to provide high bandwidth, low latency connections among functional components. Specifically, for connecting multicore processor die with stacked memory dies, point-to-point interconnections are needed and the number of memory dies will be proportional to the number of cores on the processor die. Conservatively assuming that core counts scale by a factor of 1.4X per

#### Single- and Multi-Chip Integration

generation, 1.4 times as many memory dies need to be accommodated per generation in the SiP. Simultaneously, if we assume that advances in the stacked memory technologies enable twice as many data bits to be delivered per generation and assuming that the clock rate on the processor-memory link remain unchanged, the number of bit links between the multicore die and the stacked memory dies will have to grow by a factor of 2.8X with each process generation.

As an example, at 14 nm, Intel implements 1024-bit-wide bit links as EMIBs (embedded multi-die interconnection bridge) on a silicon substrate to each HBM inside the SiP with a core count of 56. When the transition is made to hyperscaled 10 nm, the core count grows to 78 (=56 X 1.4), requiring 2048-bit wide links to each HBM and the ability to connect to 1.4 times as many HBMs. This will require finer interconnection pitches in the EMIB or other enhancements that will require additional metal layers (beyond the 4 to 6 metal layers in use now on the silicon bridge) and additional vias in the EMIBs, or alternative on-package interconnection techniques. In general, the on-chip interconnection problem may be exacerbated when dies integrating general-purpose cores and accelerators are integrated with other components, as off-die connections may be grossly limited by the physical dimensions of the die. Table 2 includes commonly used PHY options and corresponding specifications.

|                                  | Parallel I                                       | Serial Interface<br>(SerDes)                   |                                                     |  |  |

|----------------------------------|--------------------------------------------------|------------------------------------------------|-----------------------------------------------------|--|--|

|                                  | Non-Memory Memory                                |                                                |                                                     |  |  |

| Standards &<br>Specifications    | DARPA, OCP-ODSA<br>AIB, HBI, BoW                 | JEDEC<br>HBM2, HBM2E HBM3                      | IEEE 802.3, PCI-SIG, OIF<br>1G - 56G & 112G URS/XSR |  |  |

| Data Rate per Lane<br>(Gbps)     | 1 to 2 $\rightarrow$ 2 to 4 $\rightarrow$ 4 to 6 | $2.4 \rightarrow 3.2$ to $3.6 \rightarrow 6.4$ | 1.25 to 112                                         |  |  |

| I/O number per link              | 30 to 2000+                                      | 1024                                           | 2 pairs (4) 🗸                                       |  |  |

| Latency                          | Low 🗸                                            | Low 🗸                                          | High                                                |  |  |

| Interconnect reach               | Short Short Long                                 |                                                | Long 🗸                                              |  |  |

| Interconnect<br>medium type need | High dens<br>(Silicon Ir                         | Low resistance<br>(High Density Fan-Out)       |                                                     |  |  |

Table 2: Die-to-Die PHY Options in Advanced Process Nodes (R. Horner, OPC-ODSA)

3D integration can also be a promising solution if thermal, yield and reliability issues are addressed to permit stacking of memory dies and processor dies. This will be more realistic for stacking lower-power, energy-efficient integer cores targeted to specific data center applications with DRAM memory/HBM dies.

A possible SiP solution in the HPC/Data Center market will be to use tiling to decompose a large/low-yield die, such as a multicore CPU, into smaller homogeneous dies (which will have a higher yield), and build appropriate interconnections among them to realize the same throughput as the larger die. Other advantages of this approach will include the ability to distribute the heat load, efficiently distribute power, do microarchitectural innovations, etc. The possible solutions for addressing these needs are as follows:

#### Short-term (0 - 5 years):

As mentioned above, driven by the demands of on-package performance and functionality scaling, high-bandwidth interconnects are experiencing an explosive growth. Both I/O speed and density erupt unprecedentedly and result in a large variety of proprietary I/O standards. These short-term solutions will temporarily satisfy the emerging demands.

• **2.5D integration; Si-interposer and EMIB:** Embedded Multi-die Interconnect Bridge (EMIB) is an approach developed by Intel for in-package high density interconnect of heterogeneous chips. The industry refers to this application as 2.5D package integration. Instead of using a large Si interposer typically found in other 2.5D approaches (like TSMC's CoWoS and Unimicron's embedded interposer carrier), EMIB uses a very small bridge die with multiple routing layers, but without TSVs. This bridge die is embedded as part of Intel's substrate fabrication process. With further improvement and broader applications, EMIBs will continue to play a dominant role in the near future with enhancements in the choice of organic materials, number of metal layers, and improved driver/receiver circuitry for signal integrity enhancements.

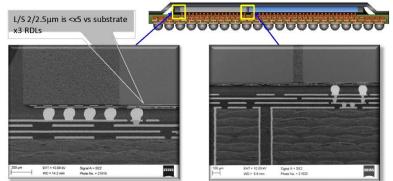

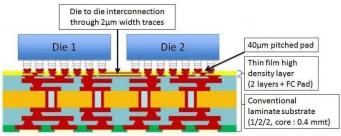

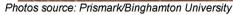

Figure 1: Embedded Multi-die Interconnect Bridge (EMIB) [1]

• **High-density organic substrate:** By combining with thin film processes, high-density flip-chip organic packaging is emerging as a potential integration carrier. 8/8um line/spacing and <50um via pitch will soon be commercially available at reasonably low cost, and 2/2um line/spacing is projected on the five-year roadmap. Various solutions are proposed, and there will be multiple options to choose as a substitution to a silicon interposer and/or EMIB-like hybrid. Even though there are still gaps – particularly line width/spacing – compared with silicon technologies, organic substrates are much easier for designs and cost much less. On the other hand, fine lines may cause RC delay due to high line resistance, as on silicon chips, and therefore there is an optimal line width number, which is roughly between 2 and 5 um.

Figure 2: Emerging high-density organic substrate [2]

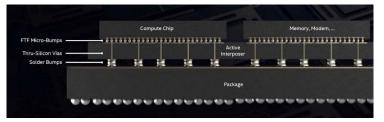

• **3D integration on the horizon:** At the end of 2018, Intel announced a 3D chip-stacking technology, called FOVEROS. It utilizes a large silicon carrier to integrate multiple chips and differs from a silicon interposer by incorporating active devices into the silicon carrier. This is a breakthrough, since the development of silicon-level 3D integration for high-performance systems had slowed down due to thermal and power delivery issues.

Figure 3: FOVEROS 3D chip stacking by Intel [3]

• Ceramic-Based Heterogeneous Carrier (CBHC): Ceramic substrates had been widely used to integrate multi-chip modules for decades until gradually replaced by organic laminates because of continuous advances in semiconductor technology. Now that system integration comes back to the package level, leading ceramics companies, such as NTK Technologies, are developing a Ceramic-Based Heterogeneous Carrier (CBHC) by taking advantage of both ceramic and organic materials. Such low-cost, large dimension, low-CTE, BA-friendly, reliable, and reworkable heterogeneous substrate technologies are expected to become commercially available in the near future.

# Longer term (5 – 15 years):

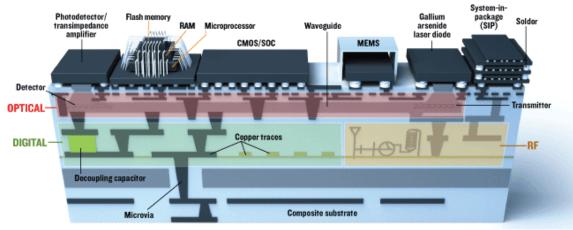

Package-level 3D integration will address the demands for performance and miniaturization, which will also be more effective in terms of scalability and cost, together with the following upcoming technologies:

- Integrated photonics with polymer waveguides and improved optical transceiver stability;

- Plasmonic interconnections;

- Optical vias for 3D integration;

• Other technologies, protocol-specific, such as embedded components.

Figure 4: 3D heterogeneous integration

Very similar scaling rules apply to the point-to-point interconnections between GPU dies and stacked memory dies or between special-function FPGA dies and stacked memory dies.

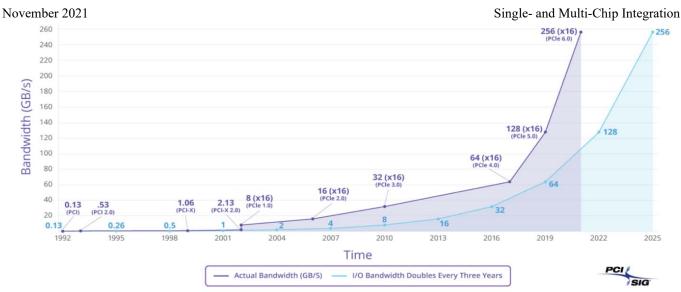

Connections to off-package interfaces and DRAM controllers on the SiP substrate can continue to rely on the PCIe standard, and the evolution path for multi-lane PCIe have been well-defined. The implementation of alternatives to direct links based on point-to-point interconnection technologies will require multiple metal layers in the silicon substrate, and the exact topologies used are specific to the SiP architecture. Signal integrity requirements for longer links in the substrate, symbol encoding, and clock synchronization issues have to be addressed here. If higher-speed serial links are used, the silicon-imposed limits on SERDES have to be observed. Photonics links will be a viable interconnection alternative for implementing high-data-rate, relatively longer links on the substrate, but this will require significant advances to be made for realizing low-power emitters whose wavelength drifts are limited with temperature variations, as well as the design of reliable detectors.

# 3. Off-package interconnections

As additional components are integrated within a single package, the demands on the off-chip interconnections go up commensurately with the number of processing elements that are integrated. The newer generation of PCIe links can possibly meet these needs, but the ultimate limitation will be imposed by the package pinout. As an example, when 1.4X more cores are accommodated on a multicore die, the off-package link count will need to go up commensurately. With a limit on the pin count, this need can be met by increasing the link data rate and multiplexing multiple logical links on a single physical link. Photonics links can be an alternative to copper links, since techniques like wavelength division multiplexing can be used to implement several connections concurrently on a single photonic link. Here again, limiting wavelength drifts becomes critical.

# **Possible Solutions**

# • Future-generation links:

Package-level system integration tends to blur the line between on-package and off-package I/O. Many I/O standards are commonly used for both I/O scenarios. PCIe is one of the most popular I/O standards, and it takes over four years for each generation evolution (doubling of the data rate). However, as PCIe Gen4 was hardly settling down in 2017, the industry had already started searching for solutions for PCIe Gen5, which is a clear indication of package-level system integration advancement. PCIe Gen5 is expected to carry 32Gbps per data channel without changing the Tx/Rx specifications. IBM and Amphenol Corporation jointly developed a new PCIe connector and demonstrated PCIe Gen5 bandwidth in early 2018, which significantly accelerates the availability of the new standard. The upcoming PCIe Gen6 will further double the data rate to 64Gbps by adopting PAM4 signaling.

Driven by package-level integration, numerous proprietary I/O standards have been emerging in recent years, such as GenZ, Omni-Path, NVLink, etc. Most are evolving towards 32Gbps in the next couple of years. Table 3 shows SERDES I/O speed, distance, and channel topologies. Off-package 56Gbps data-rate is expected by 2020 with PAM4 signaling.

Table 3: SERDES I/O speed, distance, and channel topologies (compiled from various sources)

| Parameter Ultra Short Range           |   | Very Short Range        | Short Range         | Mid Range         | Long Range           |  |

|---------------------------------------|---|-------------------------|---------------------|-------------------|----------------------|--|

| Data Rate, Gbps 32 – 112              |   | 32 - 112                | 32 - 112            | 32 - 112          | 32 - 112             |  |

| Bit Error Rate 1E-15                  |   | 1E-15                   | 1E-15               | 1E-12             | 1E-9                 |  |

| Distance, cm                          | 1 | 5                       | 15                  | 50                | 100                  |  |

| Interconnect MCM                      |   | PCB + 0 connector       | PCB + 1 connector   | PCB + 1 connector | PCB + 2 connector    |  |

| Insertion Loss, dB @ f <sub>N</sub> 3 |   | 6 (PAM4), 14 (NRZ)      | 15 (PAM4), 35 (NRZ) | 30 (PAM4)         | 27 (PAM8), 45 (PAM4) |  |

| Modulation NRZ                        |   | NRZ or PAM4 NRZ or PAM4 |                     | PAM4              | PAM4 or PAM8         |  |

| Forward Error Correction N            |   | Ν                       | Y                   | Y                 | Y                    |  |

# • Electrical/optical "flyover" cabling:

To mitigate the degradation of via and solder-joint transitions in the package and PCB, direct "flyover" cabling as shown in Figure 6 is another option for scaling channel data-rate from the current 28Gbps up to 56Gbps and 112Gbps. Compared with conventional interconnects, channel loss may be significantly reduced. However, the number of channels is limited by cable flexibility, and multiple-cable arrangement is much more complex than wiring in PCBs. Therefore, it will likely be a supplemental solution only for long-reach interconnections.

Figure 6: Electrical/optical "flyover" cabling [6]

# 4. Signal integrity issues

In general, to exploit the capabilities of a SiP without I/O bottlenecks, dense parallel connections need to be used on-package, and higher-bandwidth off-package connections operating at very high link rates become a necessity. These certainly introduce potential signal integrity problems that need to be dealt with adequately. Powerful error correction capability going beyond ECC will be necessary for critical on-package connections, and alternative symbol encoding and signal processing necessary for recovering data waveforms for off-chip links may well become the norm in very high-end, high-availability SiPs.

With growing data-rate, both loss and crosstalk increase significantly, and channel signal integrity can be compromised. Therefore, new materials, connectors/sockets, and via transitions are required to achieve link specifications. For dielectric materials, 3-4 times lower dielectric loss (compare with FR4,  $\tan\delta=0.22$ ) will be widely available, combined with smooth copper foil to mitigate skin effects. Meanwhile, a low dielectric constant (<3.2) may help reduce within-layer channel-to-channel cross-talk. For via transitions, via-stub removal by using blind vias or backdrilling is critical, and a smaller via diameter may be needed for via impedance control and cross-talk reduction. Further, signal conditioning and equalization will be widely adopted to compensate for excessive loss, ISSI, and cross-talk. For data rates beyond 50Gbps, PAM4 signaling will prevail, for much lower Nyquist frequency.

# 5. Power integrity issues

Power distribution and power quality issues become dominant as more components that operate at lower voltages (sub one Volt or close to a Volt) are integrated. In the extreme case, assuming a 200 Watt package TDP, if these components dissipate 70% of the package power (that is, 140 Watts), the current draw from the regulated source will be around 140 Amps. With many components drawing high levels of current that are placed at different positions on the substrate, a larger number of pins needs to be devoted to the power connections. Worse, inductive noise on the power connections will be significant, affecting power quality and requiring additional decoupling capacitors. Additionally, Ohmic losses may be non-negligible, affecting the overall energy efficiency.

A potential remedy for these issues will be to incorporate local voltage regulators within the package itself as a separate integrated component, but adequate cooling will need to be provided. Inductorless integrated switched-capacitor regulator technologies have certainly evolved and can be operated in a distributed configuration to provide point-of-load regulation; these are a strong contender as the best solution, whether used intra-die or intra-package. Complementing these solutions, distributed point-of-load power regulators implemented in the mainstream CMOS process technologies, that enable DVFS control and have a low setting time, appear to be an attractive solution at the die level. The microprocessor industry has been using distributed regulators on the die for the past few years and SiP-level solutions extending these are thus viable for meeting short-term needs.

Advances in low-loss discrete switching devices for power electronics (such as SiC, GaN) are likely to permeate the SiP product spectrum and offer improved efficiency, reliability and availability in power distribution systems for emerging and future SiPs.

A final solution that has the potential for scaling well with SiP complexity will be to use distributed regulators within the package that operate at higher input DC voltage and regulate down in a distributed configuration to the sub one Volt or one Volt region as needed. This solution will certainly reduce Ohmic losses on the power connections, but their benefit in terms of reducing inductive noise is not clear and may not be commensurate with the reduced current draw on the power lines to the package.

# **Issues and Challenges**

- High-performance processing chipset power rating: 300W

- High-performance graphic chipset power rating: 400-500W

- Sub-volt power supply (0.85V), maximum switching current ~300A, requires >100uF on-chip capacitance for less than 10% voltage variation

- Bring regulator closer to the silicon die

- Multi-level decoupling

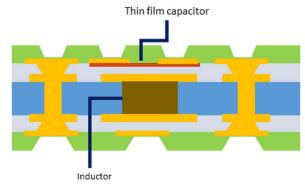

- On-package embedded capacitor/capacitance and inductor

- Operation coding for lower simultaneous switching current

# 6. Global power and thermal management

The various components integrated onto a single substrate in a SiP can each have their own power management strategy. A global power management scheme is essential to synergistically manage the power dissipation of all integrated components to not only stay within the package TDP but also to address any inevitable hot spots that may

#### Single- and Multi-Chip Integration

result. There are several ways to implement a global power management scheme, and all require the ability to sense temperature and the power dissipated within key blocks of the various dies. A dedicated controller for power management may be needed, similar to the PMU microcontrollers used in many multicore processor chips. Several power management policies are possible that use static or dynamically allocated power budgets. PMUs implementing machine learning-based global power and temperature management are also possible. This is an open area of research and may well dictate the standardization of sensor and actuator interfaces for each integrated component, including voltage regulators inside the package.

#### References

- 1. EETimes, "Intel Shows 2.5D FPGA at ISSCC", By Rick Merritt, Febuary 2017

- 2. ARS Technica, A. Usman, et, al, "Interposer Technologies for High Performance Applications", IEEE Transactions on Components, Packaging, and Manufacturing Technology pp99, March 2017

- 3. "Intel introduces Foveros: 3D die stacking for more than just memory", by Peter Bright, December 2018

- 4. Tummala, R., "Moore's Law Meets Its Match", IEEE Spectrum, 43(6), June 2006.

- 5. Smith R., "PCI Express Bandwidth to Be Doubled Again: PCIe 6.0 Announced, Spec to Land in 2021", in AnandTech, June 18, 2019

- 6. Samtec Micro FireFly Flyover System (samtec.com)

#### **Section 3: Thermal Management**

The Longevity of Moore's law has been under constant debate [1]. Many packaging experts still believe that Moore's law can hold good for at least the next 10 years due to recent technological efforts to combine functionalities horizontally and vertically into a single-chip module, commonly referred to as heterogeneous integration (HI). HI is the basis of future-generation computer systems. It refers to the assembly and placing of multiple separately manufactured components onto a single module to improve functionality and enhance operating characteristics. In such application, heat sinks are typically designed to cool multiple dies with different powers, sizes, heights, and maximum allowable temperatures in specified arrangements on electronic boards simultaneously. For several decades, electronic industries and relevant academic research communities globally have made constant efforts to develop and commercialize Moore's law [1,2], leading to many technological breakthroughs and revolutions in packaging technologies and skyrocketing thermal management challenges. These challenges are attributed to a decrease in device size and increased power consumption. With simultaneous shrinkage in size and increased heat dissipation, the flux values have increased exponentially, yet the required temperature difference coined as the thermal budget for thermal management is also reduced or unchanged, making it even more challenging for effective thermal management. Thermal management of electronic devices is important to improve the reliability of devices by maintaining silicon junction temperatures below critical safe operating temperatures. While the academic efforts on optimization of thermal solutions have been predominantly streamlined to theoretical studies, the constraints on manufacturability and reliability are not widely considered part of the optimization problem. Furthermore, owing to the multiple hotspot boundary conditions, the physics based computational modeling becomes more complex due to loss of symmetry. The challenges due to multiple hotspots will be discussed in this section, and are further analyzed in Chapter 20.

A typical thermal solution is to have a remote separable cold plate/heat sink attached to the chip with a thermal interface material (TIM). The thermal solutions for heterogeneously integrated packages, in general, can be categorized into

Technology 1 (T1)– Embedding the cooling solution onto the device (two-phase)

**Technology 2 (T2)** – Embedding the cooling solution onto the chip lid/integrated heat spreader (single- and two-phase liquid cooling).

Technology 3 (T3) – remote separable heat sink/cold plate thermal solution (Air and single-phase liquid cooling).

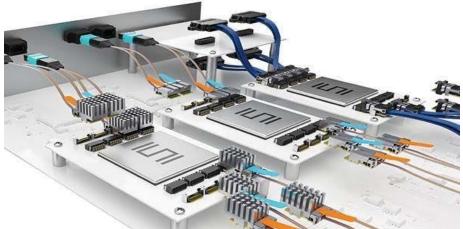

The heat transfer limit of each of the stated technologies is as shown in Figure 1.

Figure 1: Heat transfer limits of different thermal management technologies

The associated complexities and risks in implementing each of these technologies are marked on the ordinate of Figure 1. In practice for today's ongoing data center power demand, the most common cooling method takes the form of air-cooling [3]. Air-cooling is often claimed to be the most reliable technology that is of practical interest. However, in practice, air cooling suffers from low heat transfer performance and acoustic-related problems. The low heat transfer performance is attributed to low heat transfer coefficient, high inlet air temperature, and low thermal spreading due to the requirement of a larger heat sink base area. The noise issue is addressed by imposing an engineering constraint on the maximum fan velocity [4]. To address the thermal spreading issue, technologies like vapor chambers integrated with heat pipes are employed. The acoustic constraints and the allowable pressure drop dictate the limit on the maximum airflow in the system. The constraint on minimum inlet air temperature is dictated by the Telcordia GR63 standard and ASHRAE for telecom application (55°C) and data center application (45°C), respectively. With regard to easier manufacturing, plate-fin parallel-channel heat sinks are still the most widely adopted fin design. With most of the stated factors associated with air cooling having reached standard limits, only the geometric optimization of air-cooled heat sinks could help the research community define the limits of the technology under practice. Unlike the air-cooled heat sink modules, the liquid-cooled heat sinks (commonly referred to as cold plates) can perform exceptionally well due to the superior thermal properties of liquid water. However, the superior thermal performance balances with the reliability and technological risks associated with using water closer to the circuit (e.g. unfavorable dielectric strength). In a liquid-cooled module, the heat sink resistance is 10fold lower than the spreading and the TIM counterparts.

For a highly non-uniform and intense hotspot power map, there are two possible thermal solutions:

- Highly efficient thermal spreading by employing advanced vapor chamber thermal solutions

- Embedding the cooling solutions directly onto the die (hotspot-targeted)

The highly non-uniform chip power map [5] from a mechanical perspective leads to high warpage, which becomes a critical challenge. This issue also pertains to multi-chip modules. Localized heat (hotspot) is one of the significant influencers to both parametric and catastrophic reliability issues on electronic devices. Emerging chip hotspots are a major reliability concern, with heat fluxes as much as 5-6 times greater than those found elsewhere on the chip. Chip hotspots also augment thermo-mechanical stress [6] at chip-package interfaces, leading to failures during cycling. Highly localized transient chip cooling is technically challenging and costly. Furthermore, the non-uniform distribution of the localized zones leads to a much more substantial impact on the mechanical stability of the package [7]. Each material in a package responds to temperature changes differently according to its thermal expansion coefficient and generates thermomechanical stress between different materials due to a mismatch in thermal and mechanical properties. Though advanced vapor chamber heat spreading solutions can help minimize the thermal spreading resistance, they still demand a thermal interface material (TIM) between the chip and the spreader. Eliminating the TIM and other sequential conduction resistances from the chip to the coolant becomes critical from a thermomechanical perspective. In the case of multi chip modules, significant challenges involve the TIM design.

#### Single- and Multi-Chip Integration

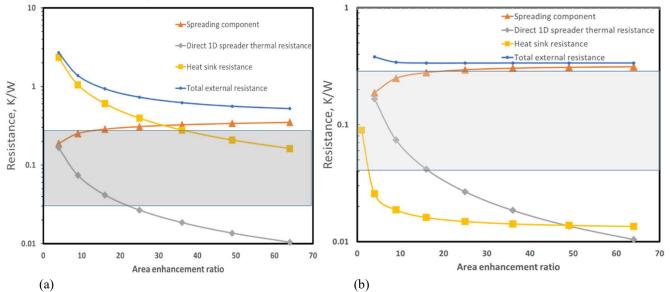

Tuckerman and Pease [8] dissipated heat flux up to 790 W/cm<sup>2</sup> for a substrate temperature rise of 71°C by etching a microchannel on the backside of the active device. However, there are practical limitations, challenges, and risks in implementing the work in practice and it requires a massive change in the existing infrastructure. Understanding the scaling limits of air and liquid cooling is essential to understand better the potential of embedding the cooling solutions onto the silicon die. Figures 2(a) and 2(b) show the limits of air and liquid cooling with increasing area ratio (AR = ratio of area of the spreader to the area of the chip). AR=1 translates to a scenario of embedded cooling. The results from the scaling analysis make it evident that the liquid cooling with AR=1 has the minimum total external resistance. Hence liquid cooling with printed fins on-chip with no additional spreader area ideally can extend the heat transfer limit of single-phase liquid cooling. However, air cooling requires a large area for effective heat dissipation and does not perform well when embedded.

Figure 2: (a) Tradeoff analysis for air cooling with variable area enhancement ratios, assuming the chip size  $Ac = 1cm^2$ , metal conductivity, k = 150W/mK, spreader thickness t = 10mm, wch = 1mm, hch=25mm, Vair=10 m/s. This figure excludes the TIM resistance. (b) Tradeoff analysis for a single phase liquid cooling scenario for a chip size  $Ac = 1 cm^2$ , metal conductivity k = 150 W/mK, Spreader thickness t = 10 mm, wch = 0.05 mm, hch=0.3 mm, Q=0.5 liters/min. The plot excludes the TIM resistance. [9]

With growing heterogeneous integration of multiple functionalities onto a single chip, there are growing regions of intense hotspots. 3D printing of fins onto the chip [10,11] is seen to be a potential solution to mitigate hotspots and achieve a minimum of the maximum chip temperature. Vahideh et al [7] numerically demonstrated single-phase heat transfer enhancement of a liquid water-based cooling system employing printing fins directly onto a chip. The fin material was pure silver. The authors demonstrated that careful optimization of the pin fin profile and shape could lead to a total chip-to-ambient thermal resistance of 0.26°C-cm<sup>2</sup>/W (compared to a separable cold plate of 0.58 °C-cm<sup>2</sup>/W) for a 4cm<sup>2</sup> uniformly heated chip under a constrained pressure drop [11]. The same technique was extended by Vahideh et al [10] to a chip with simultaneous hotspots and background heating conditions. The rationale behind the low resistance of 0.21 °C-cm<sup>2</sup>/W for four 4cm<sup>2</sup> chips under similar flow conditions. The rationale behind the low resistance was attributed to the fact that each core/hotspot had a dedicated inlet on top, thus minimizing the total resistance's caloric resistance component.

While recent efforts to explore two-phase liquid cooling using separable cold plates[12,13] for data center applications have shown remarkable performance in mitigating high heat fluxes with significant energy savings, two-phase cooling is essentially recommended for direct chip cooling using a dielectric coolant (Technology 1).

Two-phase immersion cooling could be a potential solution for highly intense and non-uniform heated devices. Boiling enhancement coatings on top of the heated surface are seen to increase the critical heat flux (CHF) and the boiling heat transfer coefficient ( $h_b$ ) simultaneously [14]. 3D printing of fin and microporous structures can be beneficial in promoting nucleation and enabling rewetting of the heated surface. The combination of fin and microstructures has been highly beneficial in the simultaneous improvement of CHF and  $h_b$  [15]. Wong et al. [16] printed lattice structures on top of a heated surface, performed pool boiling experiments, and demonstrated a critical heat flux of 107 W/cm<sup>2</sup> corresponding to a boiling heat transfer coefficient of 1.5 W/cm<sup>2</sup>K.

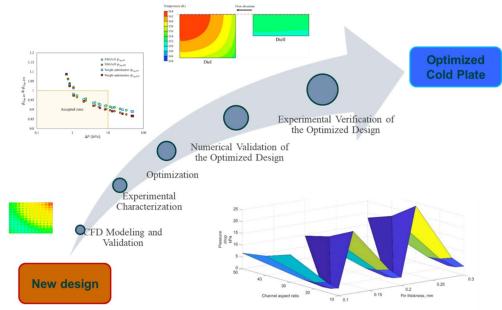

For all of the listed technologies, the optimization process of heat sinks/cold plates is as shown in Figure 3.

Figure 3: Optimization approach for the cold plate/ heat sink thermal solution

The new design or a working design is, in general, a commercially available cold plate. The working design is initially characterized numerically and experimentally. Once a benchmarked numerical model of the working design is developed, a robust multi-objective optimization is carried out employing a physics-informed machine learning process. The obtained optimal solutions are then verified numerically and experimentally.

# Challenges in computational modeling

As the hotspots become more non-uniform in a chip, the symmetry is lost, and hence the computational modeling of the thermal solutions becomes more challenging. Recently, Sharma et al. [5] published an embedded cooling-based thermal management technique for a highly non-uniform thermal power map. The authors proposed a simplified modeling approach for the thermal management solution. However, simulating the complete fluid flow and heat transfer requires detailed modeling of the entire module. Srikanth et al. [17] recently demonstrated an optimal arrangement of the non-uniformly distributed hotspot in a 3D chip package. The optimization was assisted by complete physics-based modeling due to the loss in symmetry. The modeling gets even more challenging when dynamic/transient non-uniform power maps evolve.

# References

- R. Courtland, "Transistors could stop shrinking in 2021," IEEE Spectrum, vol. 53, no. 9, pp. 9–11, Sep. 2016, doi: 10.1109/MSPEC.2016.7551335.

- [2] dcadmin, "2015 International Technology Roadmap for Semiconductors (ITRS)," Semiconductor Industry Association. https://www.semiconductors.org/resources/2015-international-technology-roadmap-for-semiconductors-itrs/ (accessed Oct. 15, 2020).

- [3] "High Powered Chip Cooling -- Air and Beyond," Electronics Cooling, Aug. 09, 2005. https://www.electronicscooling.com/2005/08/high-powered-chip-cooling-air-and-beyond/ (accessed Oct. 15, 2020).

- [4] "G. Refai-Ahmed, H. Do, Y.Hadad, S. Rangarajan, B. Sammakia, T. Cader `` ESTABLISHING THERMAL AIR-COOLED LIMIT for High Performance Electronics Devices'', In 2020 IEEE 22nd Electronics Packaging Technology Conference (EPTC), IEEE, 2020".

- [5] C. S. Sharma, M. K. Tiwari, and D. Poulikakos, "A simplified approach to hotspot alleviation in microprocessors," Applied Thermal Engineering, vol. 93, pp. 1314–1323, 2016.

- [6] © Stanford University, Stanford, and California 94305, "Limits of hotspot detection and prediction in microprocesors [sic]." https://purl.stanford.edu/jc805vt4819 (accessed Oct. 28, 2021).

- [7] J.-H. Choy, V. Sukharev, and A. Kteyan, "Advanced methodology for assessing chip package interaction effects on chip performance and reliability after chip assembly and during chip operation," Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena, vol. 38, no. 6, p. 063205, 2020.

- [8] D. B. Tuckerman and R. F. W. Pease, "High-performance heat sinking for VLSI," IEEE Electron Device Letters, vol. 2, no. 5, pp. 126–129, May 1981, doi: 10.1109/EDL.1981.25367.

- [9] Rangarajan s, Schiffres S, Sammakia Bahgat, "Scaling limits, challenges, opportunities in embedded cooling," Encyclopedia of Thermal Packaging: Thermal Packaging Tools/Ed.-in-chief Avram Bar-Cohen. World Scientific.2021.

- [10] V. Radmard et al., "Performance Analysis of Impinging Chip-Attached Micro Pin Fin Direct Liquid Cooling Package for Hotspot Targeted Applications," in 2021 20th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (iTherm), Jun. 2021, pp. 220–228. doi: 10.1109/ITherm51669.2021.9503295.

- [11] V. Radmard et al., "Multi-objective optimization of a chip-attached micro pin fin liquid cooling system," Applied Thermal Engineering, vol. 195, p. 117187, Aug. 2021, doi: 10.1016/j.applthermaleng.2021.117187.

- [12] "Khalili, Sadegh, Srikanth Rangarajan, Vadim Gektin, Husam Alissa, and Bahgat Sammakia. 'An Experimental Investigation on the Fluid Distribution in a Two-Phase Cooled Rack Under Steady and Transient Information Technology Loads.' Journal of Electronic Packaging 142, no. 4 (2020).".

- [13] "Hoang, Cong Hiep, Srikanth Rangarajan, Sadegh Khalili, Bharath Ramakrisnan, Vahideh Radmard, Yaser Hadad, Scott Schiffres, and Bahgat Sammakia. 'Hybrid microchannel/multi-jet two-phase heat sink: A benchmark and geometry optimization study of commercial product.' International Journal of Heat and Mass Transfer 169 (2021): 120920.".

- [14] G. Liang and I. Mudawar, "Review of pool boiling enhancement by surface modification," International Journal of Heat and Mass Transfer, vol. 128, pp. 892–933, Jan. 2019, doi: 10.1016/j.ijheatmasstransfer.2018.09.026.

- [15] C. M. Patil and S. G. Kandlikar, "Pool boiling enhancement through microporous coatings selectively electrodeposited on fin tops of open microchannels," International Journal of Heat and Mass Transfer, vol. 79, pp. 816–828, Dec. 2014, doi: 10.1016/j.ijheatmasstransfer.2014.08.063.

- [16] K. K. Wong and K. C. Leong, "Saturated pool boiling enhancement using porous lattice structures produced by Selective Laser Melting," International Journal of Heat and Mass Transfer, vol. 121, pp. 46–63, 2018.

- [17] S. Rangarajan, L. Choobineh, and B. Sammakia, "Supervised machine-learning approach for the optimal arrangement of active hotspots in three-dimensional integrated circuits," IEEE Transactions on Components, Packaging and Manufacturing Technology, pp. 1–1, 2021, doi: 10.1109/TCPMT.2021.3109662.

#### **Section 4: Mechanical Requirements**

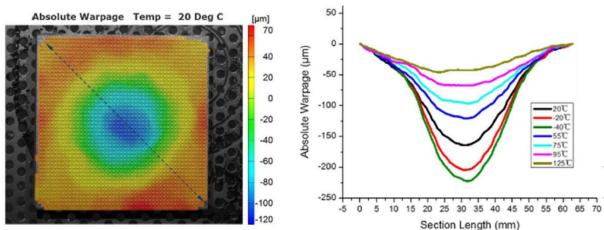

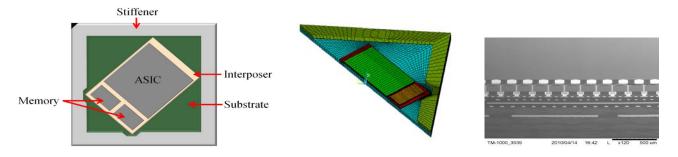

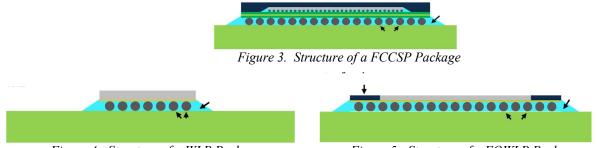

Mechanical stresses stem from differential thermal expansion of different materials within a package built-in during assembly and fabrication. Warpage is a manifestation of physical deformation and built-in stresses. Warpage engineering is thus an essential part of mechanical stress management and is essential to packaging in general to ensure that packages can be assembled into subsequent applications.

#### Warpage Engineering and Stress Management

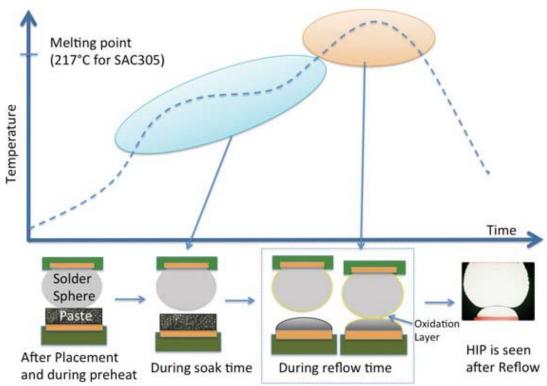

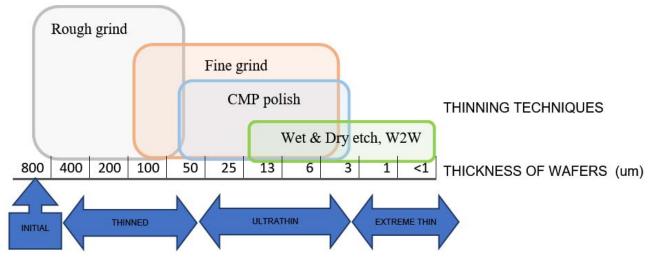

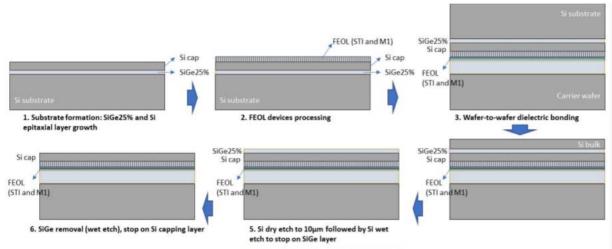

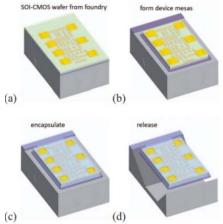

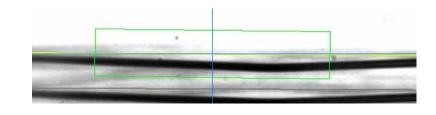

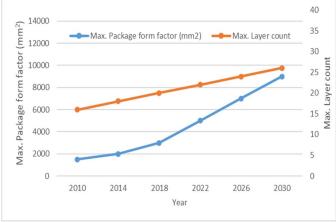

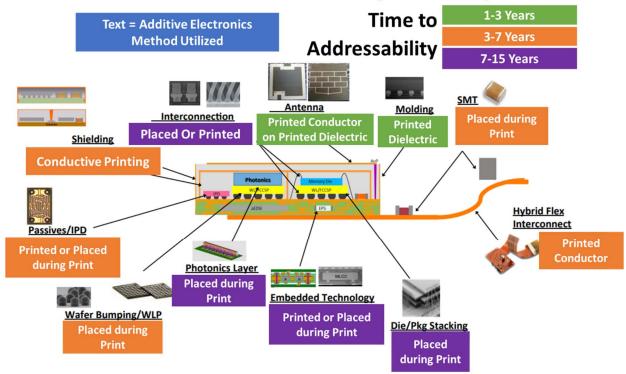

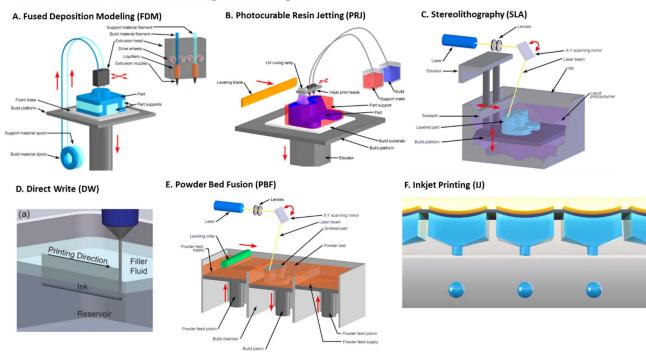

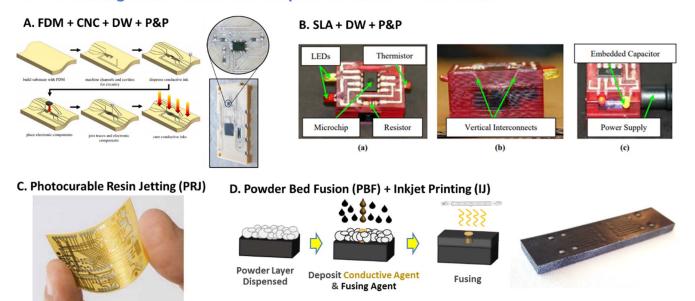

Warpage engineering has long been an integral part for electronics packaging in both reliability and manufacturing for high-performance package fabrication and assembly as well as for mobile and consumer products and their assemblies. As the form factors gets thinner and smaller, yet higher in power consumption, understanding warpage behaviors during fabrication processes and service life becames essential for successful product engineering, from design to development qualification and volume manufacturing.