Advanced Manufacturing &

Multichip Integration TWG

Technical Working Group

February 22,2024

## Today's Speakers

Bill Chen

ASE Group

Kris Erickson *META*

Sheng Li Intel

Abhijit Dasgupta *UMD*

Lei Shan *Ampere*

Benson Chan Binghamton Univ.

Annette Teng SUNY Polytechnic

Ivy Qin

Kulicke and Soffa Industries

Mark Gerber ASE Group

Srikanth Rangarajan Binghamton Univ.

#### Advanced Manufacturing & Multichip Integration

1. Electrical Performance

2. Thermal Management

3. Mechanical Engineering

4. Adv Manufacturing & Package Assembly

5. Wire bond Innovations

6. Flip Chip & Hybrid Bonding

7. Advanced Substrate

8. Additive Manufacturing

9. Reliability (Spun-Off: full TWG 2021)

10. Solder & Electromigration

Lei Shan

Srikanth Rangarajan

**Benson Chan**

**Annette Teng**

Ivy Qin

Mark Gerber

Sheng C Li

Kris Erickson

Abhijit Dasgupta

**Eric Cotts**

William (Bill) Chen & Annette Teng TWG Chair & Co-Chair

#### SINGLE & MULTICHIP ROADMAP METRICS

| Year of Production                           | 2022      | 2023      | 2024      | 2025      | 2026      | 2027      | 2028      |

|----------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| On-chip feature size (nm)                    |           |           |           |           |           |           |           |

| Memory (DDR/HBM)                             | 7         | 5         | 5         | 5         | 3         | 3         | 3         |

| Smart Phone / Laptop                         | 5         | 3         | 3         | 3         | 2         | 2         | 2         |

| High-performance (note1), chiplet/monolithic | 5         | 3         | 3         | 3         | 2         | 2         | 2         |

| Core Voltage (Minimum Volts)                 |           |           |           |           |           |           |           |

| Memory (DDR/HBM)                             | 1.1       | 1         | 1         | 1         | 0.9       | 0.9       | 0.9       |

| Smart Phone / Laptop                         | 0.8       | 0.75      | 0.75      | 0.75      | 0.7       | 0.7       | 0.7       |

| High-performance                             | 0.8       | 0.75      | 0.75      | 0.75      | 0.7       | 0.7       | 0.7       |

| Package Pin count Maximum                    |           |           |           |           |           |           |           |

| Memory (DDR/HBM)                             | 288/3200  | 288/3200  | 288/3200  | 288/3200  | 350/4700  | 350/4700  | 350/4700  |

| Smart Phone / Laptop                         | 1212/7000 | 1275/7600 | 1275/7600 | 1275/7600 | 1396/8400 | 1396/8400 | 1396/8400 |

| High performance (note3)                     | 7800      | 7800      | 9600      | 9600      | 9600      | 11200     | 11200     |

| Minimum Package Dimension (mm)               |           |           |           |           |           |           |           |

| Memory (DDR/HBM)                             | 133/10    | 133/10    | 133/10    | 133/10    | 133/12    | 133/12    | 133/12    |

| Smart Phone / Laptop                         | 50        | 55        | 55        | 55        | 60        | 60        | 60        |

| High-performance                             | 87        | 87        | 95        | 95        | 95        | 110       | 110       |

| Performance: On-Chip                         |           |           |           |           |           |           |           |

| Memory (DDR/HBM), MHz                        | 800       | 1000      | 1000      | 1200      | 1200      | 1600      | 1600      |

| Smart Phone / Laptop, GHz                    | 3.2       | 4         | 4         | 4.8       | 4.8       | 5.2       | 5.2       |

| High-performance, GHz                        | 8         | 8         | 9.6       | 9.6       | 11.2      | 11.2      | 11.2      |

| Interconnect: Chip-to-Chip (note4)           |           |           |           |           |           |           |           |

| Memory (DDR/HBM), Gb/s                       | 4.8/3.6   | 4.8/5.2   | 5.6/6.4   | 6.4/7.2   | 7.2/8.0   | 8.0/9.6   | 9.6/9.6   |

| Smart Phone / Laptop, Gb/s                   | 100       | 100       | 100       | 200       | 200       | 200       | 200       |

| High-performance, Gb/s                       | 32        | 32        | 32        | 64        | 64        | 64        | 112       |

| Interconnect: Pkg-to-Board                   |           |           |           |           |           |           |           |

| Memory (DDR/HBM), Gb/s                       | 8/6.4     | 8/6.4     | 9.6       | 12.8      | 16        | 25        | 25        |

| Smart Phone / Laptop, Gb/s                   | 100       | 100       | 100       | 200       | 200       | 200       | 200       |

| High-performance, Gb/s                       | 56        | 56        | 64        | 64EEE     | 112       | 112       | 224       |

## UCIe to Enable Low-Power & High-Bandwidth Chiplet Integration

| Characteristics / KPIs         | Standard<br>Package | Advanced<br>Package | Comments                                                                |

|--------------------------------|---------------------|---------------------|-------------------------------------------------------------------------|

| Characteristics                |                     |                     |                                                                         |

| Data Rate (GT/s)               | 4, 8, 12, 16, 24,   | 32                  | Lower speeds must be supported -interop (e.g., 4, 8, 12 for 12G device) |

| Width (each cluster)           | 16                  | 64                  | Width degradation in Standard, spare lanes in Advanced                  |

| Bump Pitch (um)                | 100 – 130           | 25 - 55             | Interoperate across bump pitches in each package type across nodes      |

| Channel Reach (mm)             | <= 25               | <=2                 |                                                                         |

| Target for Key Metrics         |                     |                     |                                                                         |

| B/W Shoreline (GB/s/mm)        | 28 – 224            | 165 – 1317          | Conservatively estimated: AP: 45u for AP; Standard: 110u;               |

| B/W Density (GB/s/mm²)         | 22-125              | 188-1350            | Proportionate to data rate (4G – 32G)                                   |

| Power Efficiency target (pJ/b) | 0.5                 | 0.25                |                                                                         |

| Low-power entry/exit           | 0.5ns <=16G, 0.5    | 5-1ns >=24G         | Power savings estimated at >= 85%                                       |

| Latency (Tx + Rx)              | < 2ns               |                     | Includes D2D Adapter and PHY (FDI to bump and back)                     |

| Reliability (FIT)              | 0 < FIT (Failure I  | n Time) << 1        | FIT: #failures in a billion hours (expecting ~1E-10) w/ CXi Flit Mode   |

INTEGRATION ROADMAP

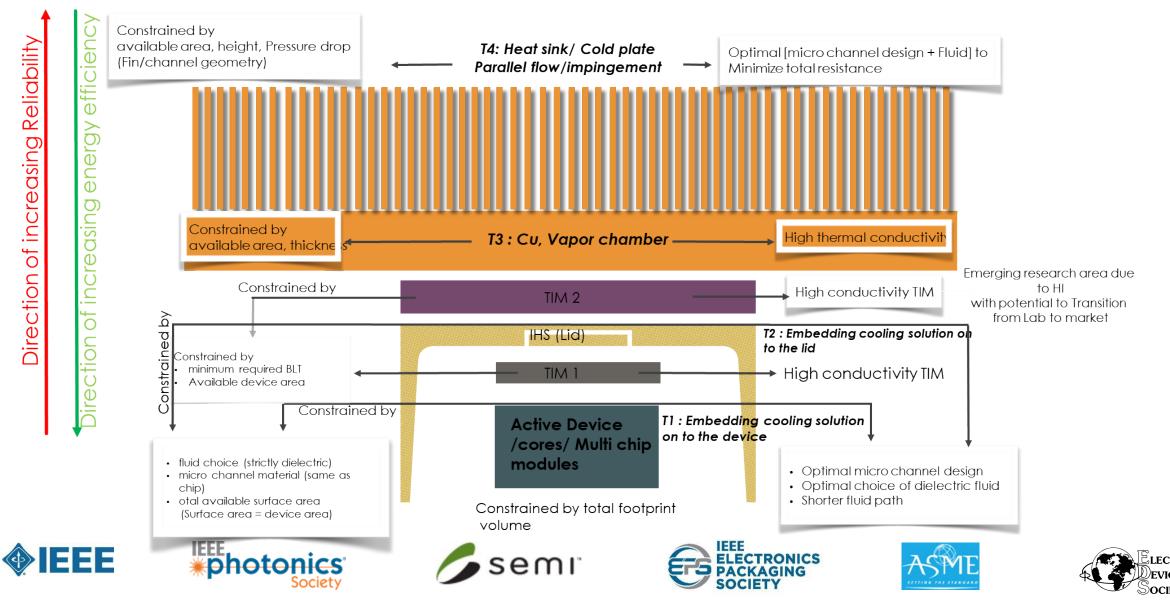

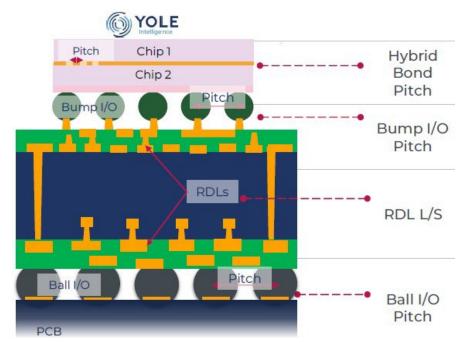

#### Optimization Opportunities for heterogeneous integrated packages

Constrained by overall footprint and height of the package module

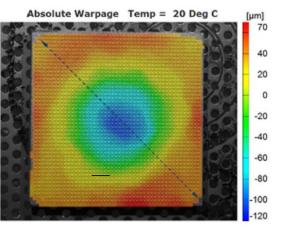

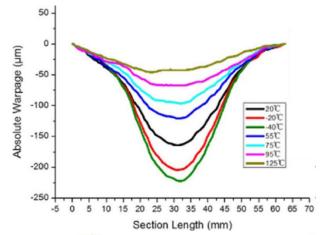

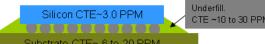

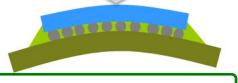

#### Warpage Engineering, Chip-Package-Interaction (CPI)

#### Warpage Engineering

Assembly stress due to warpage is the largest contributor to failures in packaging. Some of the variables leading to the warpage include substrate materials, copper distribution (wiring density), number of layers, underfill material, die thickness, processing temperatures, humidity...

Reducing warpage and stress will contribute to higher yields and better reliability. As interconnect pitches go down, the warpage window for packages will be reduced

Step1: Silicon attach to substrate at Solder Reflow Temperature ~230°C

Step2: Cool down to room temperature

Step3: Heat back to underfill temperature  $(150 \sim 200^{\circ}\text{C})$

Step4: Cool down again

## WARPAGE REDUCTION ROADMAP

Table 2: Warpage Allowance across two market segments

|          | Year of<br>Production | 2018         | 2019           | 2020           | 2023           | 2026           | 2029           | 2030           |

|----------|-----------------------|--------------|----------------|----------------|----------------|----------------|----------------|----------------|

|          | Pitch (mm)            |              |                |                |                |                |                |                |

|          | 4.0                   | -0.13, +0.21 | -0.11, +0.18   | -0.11, +0.18   | -0.11, +0.18   | -0.10, +0.16   | -0.08,+0.16    | -0.08,+0.17    |

|          | 1.0                   | -0.13, +0.20 | -0.11, +0.18   | -0.11, +0.18   | -0.11, +0.18   | -0.10, +0.15   | -0.08,+0.15    | -0.08,+0.16    |

|          | 0.8                   | -0.13, +0.21 | -0.11, +0.18   | -0.11, +0.18   | -0.11, +0.18   | -0.10, +0.16   | -0.08,+0.16    | -0.08,+0.17    |

| ပ္       | 0.8                   | -0.10, +0.10 | -0.09, +0.09   | -0.09, +0.09   | -0.09, +0.09   | -0.08, +0.08   | -0.07, +0.07   | -0.07, +0.07   |

| FPC      | 0.65                  | -0.10, +0.10 | -0.09, +0.09   | -0.09, +0.09   | -0.09, +0.09   | -0.08, +0.08   | -0.07, +0.07   | -0.07, +0.07   |

|          | 0.00                  | -0.09, +0.09 | -0.08, +0.08   | -0.08, +0.08   | -0.08, +0.08   | -0.07, +0.07   | -0.065, +0.065 | -0.065, +0.065 |

|          | 0.5                   | -0.09, +0.09 | -0.08, +0.08   | -0.08, +0.08   | -0.08, +0.08   | -0.07, +0.07   | -0.065, +0.065 | -0.065, +0.065 |

|          | 0.5                   | -0.08, +0.08 | -0.07, +0.07   | -0.07, +0.07   | -0.07, +0.07   | -0.065, +0.065 | -0.06, +0.06   | -0.06, +0.06   |

|          | 0.4                   | -0.08, +0.08 | -0.07, +0.07   | -0.07, +0.07   | -0.07, +0.07   | -0.065, +0.065 | -0.06, +0.06   | -0.06, +0.06   |

|          | 0.4                   | -0.07, +0.07 | -0.065, +0.065 | -0.065, +0.065 | -0.065, +0.065 | -0.06, +0.06   | -0.055, +0.055 | -0.055, +0.055 |

|          | 0.3                   | -0.07, +0.07 | -0.065, +0.065 | -0.065, +0.065 | -0.065, +0.065 | -0.06, +0.06   | -0.055, +0.055 | -0.055, +0.055 |

| <u>o</u> | 0.3                   | -0.06, +0.06 | -0.055, +0.055 | -0.055, +0.055 | -0.055, +0.055 | -0.05, +0.05   | -0.045,+0.045  | -0.045,+0.045  |

| <u> </u> | 0.25                  |              | -0.055, +0.055 | -0.055, +0.055 | -0.055, +0.055 | -0.05, +0.05   | -0.045,+0.045  | -0.045,+0.045  |

| Mobile   | 0.23                  |              |                | -0.055, +0.055 | -0.055, +0.055 | -0.05, +0.05   | -0.045,+0.045  | -0.045,+0.045  |

| _        | 0.2                   |              |                | -0.055, +0.055 | -0.055, +0.055 | -0.05, +0.05   | -0.045,+0.045  | -0.045,+0.045  |

|          | 0.2                   |              |                |                | -0.045,+0.045  | -0.045,+0.045  | -0.045,+0.045  | -0.045,+0.045  |

|          | 0.15                  |              |                |                | -0.045,+0.045  | -0.045,+0.045  | -0.045,+0.045  | -0.045,+0.045  |

|          | 0.15                  |              |                |                | -0.025,+0.025  | -0.025,+0.025  | -0.025,+0.025  | -0.025,+0.025  |

|          | 0.4                   |              |                |                | -0.025,+0.025  | -0.025,+0.025  | -0.025,+0.025  | -0.025,+0.025  |

|          | 0.1                   |              |                |                |                | -0.020,+0.020  | -0.020,+0.020  | -0.020,+0.020  |

Manufacturable solutions exist, and are being optimized Manufacturable solutions are known

Interim solutions are known

Manufacturable solutions are NOT known

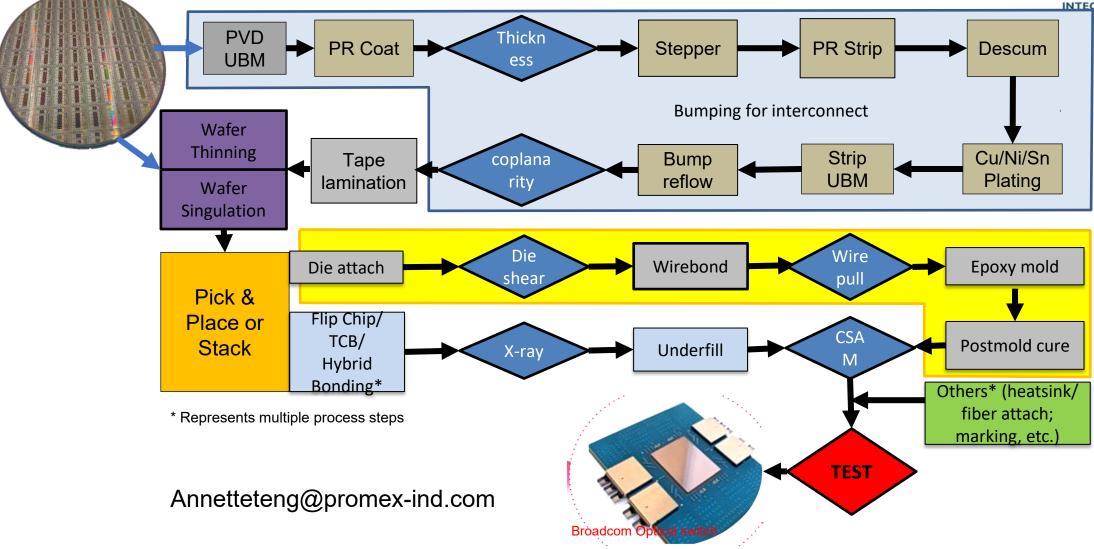

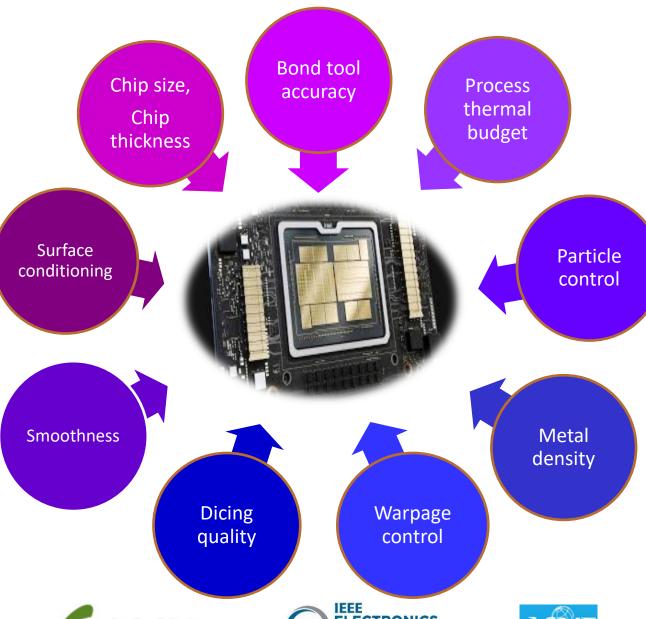

## HI Single and Multi Chip Manufacturing

## HI ASSEMBLY KEY CHALLENGES

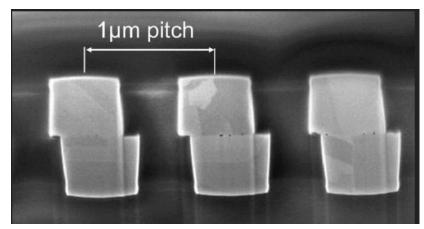

1μm pitch

Source: Leti

When pushing the limit,

there's no room for error

Annetteteng@promex-ind.com

S. W. Liang, Gene C. Y. Wu, K. C. Yee, C. T. Wang, Ji James Cui, and Douglas C. H. Yu "High Performance and Energy Efficient Computing with Advanced SolCTM Scaling" 2022 ECTC, Taiwan Semiconductor Manufacturing Company

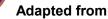

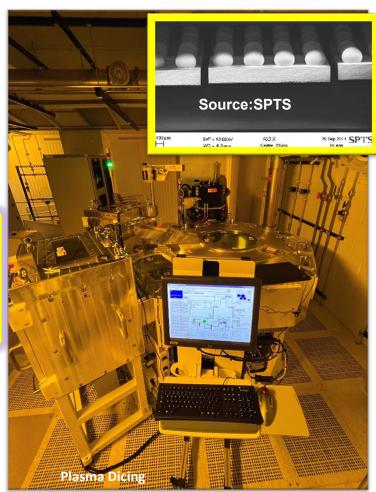

#### WAFER SINGULATION

## Increased Interconnect Density

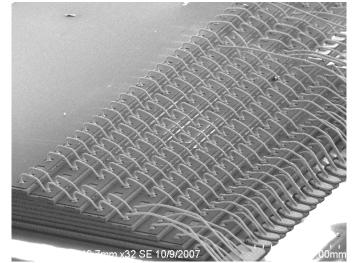

The finest inline pitch of wire bonding has remained around 35um. However, wire bonding interconnect density continuously increases through higher level of system integration such as SiP, stack die and Multi-tier packages.

30kV 20.4mm x35.8E(L) 1,00mm

SiP with Die to Die Wire Bond Interconnect

High Density Multi-tier Package

Stacked Memory Device

## Flip Chip Interconnect Pitch Roadmap –HIR 2023

| Table HI-4 Chip-to-package Substrate Technology Requ | uirements | (Update | d Nov 202 | 3)    |       |       |       |       |       |       |

|------------------------------------------------------|-----------|---------|-----------|-------|-------|-------|-------|-------|-------|-------|

| Year of Production                                   | 2018      | 2019    | 2020      | 2021  | 2022  | 2023  | 2025  | 2028  | 2031  | 2034  |

| Flip Chip Pitch                                      |           |         |           |       |       |       |       |       |       |       |

| Flip Chip- Large Body Solder >12mm Sq Die            | 135       | 130     | 130       | 130   | 130   | 130   | 130   | 130   | 130   | 130   |

| Flip Chip- Small Body Solder <12mm Sq Die            | 135       | 130     | 130       | 130   | 130   | 130   | 130   | 130   | 130   | 130   |

| Flip Chip - Cu Pillar Small Body <12mm Sq Die        | 40/80     | 30/60   | 30/60     | 30/60 | 30/60 |       | 15/30 | 15/30 | 15/30 | 15/30 |

| (Periphery Staggered, Inline Same as large Body Cu   | 40/00     | 30/00   | 30/00     | 30/00 | 30/00 | 20/40 | 15/50 | 13/30 | 15/50 | 15/50 |

| Flip Chip- Cu Pillar Large Body >12mm Sq Die         | 120       | 110     | 110       | 110   | 110   | 105   | 100   | 90    | 90    | 80    |

| Flip Chip Solder - COW                               | 50        | 50      | 50        | 50    | 50    | 50    | 50    | 50    | 50    | 50    |

| Flip Chip Cu Pillar -COW (Chiplets on Si)            | 40        | 40      | 40        | 35    | 30    | 30    | 22    | 16    | 13    | 10    |

| Flip Chip Cu Pillar -COW (Chiplets on RDL)           | 50        | 50      | 45        | 45    | 45    | 45    | 40    | 40    | 30    | 30    |

| Wafer to Wafer Cu to Cu Interconnect                 | 5         | 5       | 5         | 2     | 2     | 2     | 2     | 1     | 1     | 1     |

| Die to Wafer Cu to Cu Interconnect (Hybrid)          | 30        | 20      | 20        | 9     | 9     | 9     | 6     | 6     | 3     | 3     |

| Embedded Die In Substrate Interconnect Pitch         | 120       | 120     | 120       | 120   | 90    | 70    | 60    | 50    | 50    | 50    |

| Manufacturable solutions exist, and are being op     | timized   |         |           |       |       |       |       |       |       |       |

| Manufacturable solutions are                         | known     |         |           |       |       |       |       |       |       |       |

| Interim solutions are                                | known     | •       |           |       |       |       |       |       |       |       |

| Manufacturable solutions are NOT                     | known     |         |           |       |       |       |       |       |       |       |

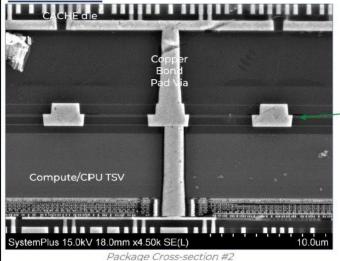

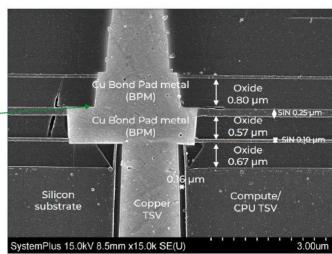

**Hybrid Bonding Enabling Next**

**Generation of Chiplets**

# 129

2024

2025

2026

Millions of Chiplet Packages

2023 Data Source: Techsearch International

2022

#### Wafer to Wafer Bonding GRATION ROADMAP

Source: Power Pulse

**Die To** Wafer **Bonding** Hybrid Bond

Interface

9um Pitch

Source: Yole Development

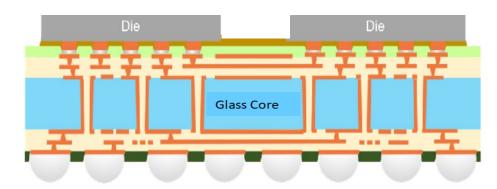

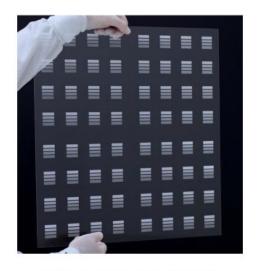

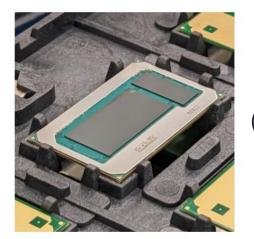

### Glass Core Substrate

(Source: Intel)

Glass Panel with Through Glass Vias (TGV)

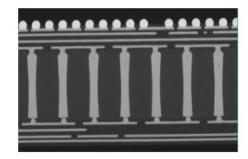

X-section of a substrate test vehicle with 3 RDLs and 75um TGVs for client products

Glass core substrates enable significant improvement to both electrical and mechanical properties

- ➤ Tunable Modulus and CTE closer to silicon → Large form factor enabling

- ➤ Dimensional stability → Improved feature scaling

- ➤ Low Loss → High speed signaling

- ➤ High (~10x) through-hole density → Improved routing and signaling

- ➤ Higher Temperature Capability → Advanced integrated power delivery

(Source: Intel)

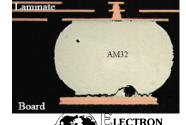

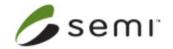

## Additively Manufactured Electronics (AME)

HETEROGENEOUS INTEGRATION ROADMAP

AME = Printed Conductor + (Printed/Existing) Dielectric + (optional) Additional Processes and with permissions from IDTechEx

Printing Methods for Electronics: Resolution vs Throughput

#### Direct-write & Conformal\*\*

Dispensing & Extrusion Print

#### Non-contact Jetting Methods

Inkjet Print

Aerosol Print

Electrohydrodynamic Print

Piezo-Valve Jetting

Laser Induced Forward Transfer (LIFT)

\*\* can deposition on 2D or 3D substrate

#### **3D Print Methods**

Fused Deposition Modeling SLA (Stereolithography) 2-photon SLA Digital Light Processing (DLP) Powder Bed Fusion

#### Contact 2D Print Methods\*

Screen/Stencil Print Gravure Print Flexographic Print

\* 2D only substrate

#### **Additively Manufactured Electronics (AME)**

#### Structural Electronics

**AME Deposition**

Dot Deposition

Line Deposition

**Area Deposition**

Pick & Place Laser Direct Structuring (LDS) Electroplating

#### In-Mold Electronics

Pick & Place Thermoforming

#### Flexible Hybrid Electronics (FHE)

Pick & Place Solder

Deposition

Lithographically Defined

Features

Over-molding

#### Additional Supporting Processes

Pick & Place (Si, passives, etc.)

Curing/Sintering

3D Scanning

Metrology

Subtractive (Laser, Milling)

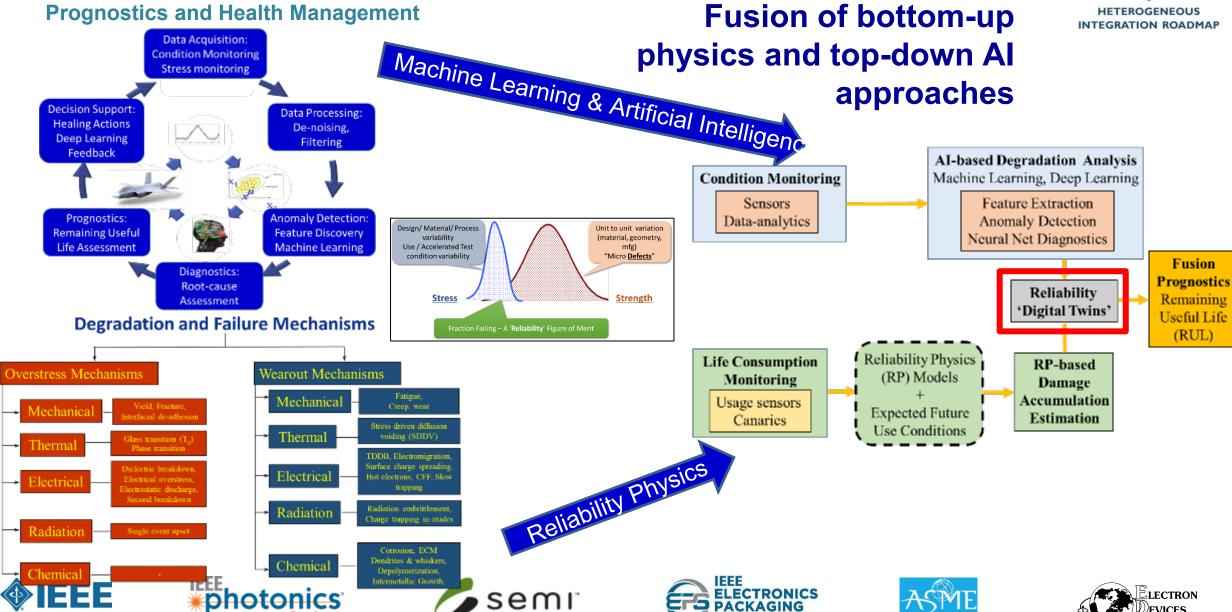

## HI System reliability

#### Modes/Mechanisms/Models for degradation & failure

| <b>Multiphysics</b> |                | Multiscale<br>Integration | Multi Physics                                                              | Elect                                                                                                    | rical Stress                                                                                                                  | SI/PI (Electrical<br>Performance)                                             | Thermal Analysis                                                                              | Mod                                                                                                     | isture                                                                                                              | Thermal Mechan                                                                                                                                                                                                               | ical Stress                                                                                                                     | Med                                                                             | anical Stress                                                                                                                         | Thermal<br>Interaction<br>with SI/PI                               | Stress<br>Interaction<br>with SI/PI                                                                    | Simulatio                                                                                                              | on/Modelling and Co-C                                                                               | sign Flows                                                                                                                         | Manufacturing<br>Variability | Material<br>Property<br>and<br>Variability |

|---------------------|----------------|---------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------|

|                     |                | integration               |                                                                            | Failure Modes                                                                                            | Failure Mechanism<br>and Reliability Models                                                                                   |                                                                               |                                                                                               | Failure Modes                                                                                           | Failure Mechanism<br>and Reliability<br>Models                                                                      | Failure Modes                                                                                                                                                                                                                | Failure Mechanism and<br>Reliability Models                                                                                     | Failure Modes                                                                   | Failure Mechanism<br>and Reliability<br>Models                                                                                        |                                                                    |                                                                                                        | Failure Modes                                                                                                          | EDA Flows                                                                                           | PDK/ADK                                                                                                                            |                              |                                            |

| Devices<br><u>a</u> | Transistor     | FinFET and GAA            | Leakage current,<br>ripple currents,<br>unstabel<br>performance and<br>ESD | N/PBTI models with<br>recovery; HCI model;<br>TDDB Weibull model;<br>Oxide & junction<br>breakdown model | Transistor<br>SPICE                                                                                                           | FinFET SHE                                                                    | No known failures                                                                             | None                                                                                                    | FinFET SHE channel stress;<br>µBump/C4 bump/TSV; system<br>level stresses                                           | FinFET SHE Models; CPI<br>Model; Piezo-electrical<br>models                                                                                                                                                                  | No known<br>failures                                                                                                            | None                                                                            | SHE effect on<br>SPICE<br>parameters                                                                                                  | Influence of<br>Si stress on<br>SPICE<br>paramters                 | Effects of<br>degradation<br>mechanisms and<br>process variabilities<br>on electrical<br>functionality | Cadence; Relxpert;<br>Mentor Graphics                                                                                  | Integrate of<br>degradation models<br>into Device SPICE<br>Model                                    |                                                                                                                                    |                              |                                            |

|                     |                |                           | MEOL/BEOL<br>Metal/Via /ELK                                                | Electromigration;<br>Inter Layer<br>Dielectric ELK<br>Breakdown; MEOL<br>Oxide Breakdown;<br>EOS         | Electromigration<br>model; Dielectric<br>breakdown model                                                                      | Extraction of<br>RLC Model                                                    | Joule Heating<br>simulation; SHE<br>effects on<br>MEOL/BEOL                                   | Pad and underline<br>metal corrosion;<br>Cu/ELK<br>delamination<br>3. Cu loss/diffusion                 | Electrochemical<br>corrosion; interface<br>degradation due to<br>moisture<br>absorption; Barrier<br>metal oxidation | SHE failure in Cu/ELK, MEOL, BEOL,<br>µBurnp, TSV; RDL failures from<br>package stress, Cu fatigue;<br>LowK/ELK layer cracking &<br>delamination                                                                             | Creep induced voiding; CTE<br>mismatch; SHE induced<br>localized thermal cycling                                                | LowK/ELK<br>layer cracking<br>&<br>delamination                                 | Fatige by bending                                                                                                                     | Joule/SHE<br>temp effects<br>on RLC                                | Effect of<br>Cu/ELK stress<br>on RLC                                                                   | CPI induced Cu/ELK<br>cracking: IHE/SHE<br>stresses; stress from<br>bumps/TSV/RDL &<br>Packaging                       | Ansys Mentor                                                                                        |                                                                                                                                    |                              |                                            |

|                     |                |                           | FBEOL<br>RDL/Dielectric                                                    | RDL/UBM<br>Electromigration                                                                              | Electromigration                                                                                                              | Extraction of<br>RDL RLC Model                                                | BEOL Joule/SHE<br>effect on RDL<br>temperature                                                | Cu dedrite                                                                                              | Electro-chemical corrosion                                                                                          | RDL cracking                                                                                                                                                                                                                 | μbump/TSV/ Package/<br>Board effects on RDL stress                                                                              |                                                                                 |                                                                                                                                       | Effect of RDL<br>temp on<br>electrical<br>model                    | Effect of RDL<br>stress on<br>electrical<br>model                                                      | CPI/CBPI induced<br>failures: RDL cracking<br>& delamination                                                           | Effect of temp and<br>stress on RDL EM                                                              |                                                                                                                                    |                              |                                            |

| Š                   |                |                           | Au/Cu<br>Wirebonding                                                       | Electromigration                                                                                         |                                                                                                                               |                                                                               |                                                                                               | IMC Corrosion                                                                                           |                                                                                                                     | Bond wire fatigue                                                                                                                                                                                                            |                                                                                                                                 | Cu/ELX<br>cracking                                                              | Bonding force<br>models                                                                                                               |                                                                    |                                                                                                        |                                                                                                                        |                                                                                                     |                                                                                                                                    |                              |                                            |

| Multiscal           | Interconnects  | Interconnects             | μΒυπρ/C4<br>Βυπρ/UBM                                                       | Electromigration induced voids                                                                           | Black's model;<br>Mutiphysics EM model<br>including eletron,<br>thermal gradient,<br>stress gradient and<br>atomic diffusion  | µbump<br>electrical<br>model                                                  | Die Internal<br>Joule/SHE temp<br>effect &<br>external temp<br>effect on bump<br>temperature  | UBM delamination                                                                                        | Galvanic effect<br>(electro-chemical<br>reaction)                                                                   | Bump joint cracking;<br>Under Bump ELK cracking; Under<br>pad cracking in substate                                                                                                                                           | CTE mismatch induced<br>stress;<br>Fatigue                                                                                      | Tensile stress<br>causes bump<br>peel; cracks at<br>ubump; UBM<br>and interface | Fracture/fatigue<br>from shock, drop,<br>impact, Vibr; e.g. in<br>die attach, dielectric<br>layer, inter-poser,<br>UBM, solder joints | Effect of temp<br>on bump<br>electrical<br>model                   | Effect of<br>bump stress<br>on electrical<br>model                                                     | Multi Physics Bump<br>EM - local current,<br>temp, temp gradient<br>and stress effect on<br>µbump EM                   | Bump fatigue: effect<br>of local temp &<br>stress on fatigue life                                   | Package material                                                                                                                   |                              |                                            |

|                     |                |                           | TSV/Interposer/<br>EMIB                                                    | Electromigration;<br>Barrier Dielectric<br>breakdown                                                     | Black's model;<br>Mutiphysics EM model<br>including electron,<br>thermal gradient,<br>stress gradient and<br>atomic diffusion | TSV electrical<br>model                                                       | Internal Joule/SHE<br>temp effect on the<br>TSV temp;<br>External temp effect<br>on TSV temp. |                                                                                                         |                                                                                                                     | Cu pumping/TSV pop up                                                                                                                                                                                                        | Cu extraion due to CTE<br>mismatch with St;<br>plastic rachetting at high<br>temp                                               |                                                                                 |                                                                                                                                       | Effect of TSV<br>temp on<br>electrical<br>model                    | Effect of TSV<br>stress on<br>electrical<br>model                                                      | TSV EM response to<br>local current, temp<br>field and stress; TSV<br>Pop out and effects<br>on TSV/Si<br>delamination | Barrier breakdown -<br>How does<br>voltage/current,<br>temp and stress<br>affect TSV barrier<br>BD? | thermal/mechanical<br>properties; Die metal<br>stack and<br>thermal/mech<br>properties; µBump/CA<br>bump/TSV thermal<br>mechanical |                              |                                            |

|                     |                |                           | Passivation                                                                | Passivation<br>cracking                                                                                  | EOS induced cracking                                                                                                          |                                                                               |                                                                                               | Passivation cracking<br>& delamination;<br>underfil/Mold<br>compound<br>delamination                    |                                                                                                                     | Passivation cracking                                                                                                                                                                                                         | CPI stress in SIN                                                                                                               |                                                                                 |                                                                                                                                       |                                                                    |                                                                                                        |                                                                                                                        |                                                                                                     | fracture criteria; Void<br>initiation and<br>propagation criteria;<br>interconnect<br>fatigue/creep model;                         |                              |                                            |

|                     |                |                           | Underfill                                                                  |                                                                                                          |                                                                                                                               |                                                                               |                                                                                               | Underfill to<br>die/substrate<br>delamination;<br>underfill swelling                                    | Moisture<br>degradation in<br>underfill & at<br>interfaces                                                          | Bump joint cracking                                                                                                                                                                                                          | Solder joint fracture and fatigue due to underfill expansion                                                                    |                                                                                 |                                                                                                                                       |                                                                    |                                                                                                        |                                                                                                                        |                                                                                                     | Package Interface<br>fracture criteria;<br>Moisture diffusion<br>and vapor pressure                                                |                              |                                            |

|                     | Packaging/     |                           | High Density<br>Substrate                                                  | Metal trace<br>electromigration                                                                          |                                                                                                                               | Package<br>Substrate RLC<br>model<br>extraction                               | Co-thermal sim<br>from die to package                                                         | Metal trace                                                                                             |                                                                                                                     | Metal trace/via cracking                                                                                                                                                                                                     |                                                                                                                                 |                                                                                 |                                                                                                                                       | Thermal -<br>electrical<br>perfromance<br>interactions             | Mechanical-<br>electrical<br>performance<br>interactions                                               | Cu trace EM - effect<br>of local current, temp<br>and stress                                                           | Thermal & mechanical effect on Cu trace/via cracking                                                | model; IMC<br>thermal/mech/electric<br>al properties;<br>Photonics optical<br>properties                                           |                              |                                            |

|                     | r ackaging/    | Packaging /System         | Wafer Level<br>Package                                                     |                                                                                                          |                                                                                                                               |                                                                               |                                                                                               |                                                                                                         |                                                                                                                     | Warpage                                                                                                                                                                                                                      |                                                                                                                                 |                                                                                 |                                                                                                                                       |                                                                    |                                                                                                        |                                                                                                                        |                                                                                                     |                                                                                                                                    |                              |                                            |

|                     | System         |                           | Eanout Package  2.x/2.5D Interposer Package (CoWoS and EMIB, etc)          |                                                                                                          |                                                                                                                               |                                                                               |                                                                                               |                                                                                                         |                                                                                                                     | Warpage Warpage; Embedded die delamination from substrate & sidewall; pvia & pbump cracking & delamination; Solder/TIM delamination                                                                                          |                                                                                                                                 |                                                                                 |                                                                                                                                       |                                                                    |                                                                                                        |                                                                                                                        |                                                                                                     | _                                                                                                                                  |                              |                                            |

|                     |                |                           | 3D Package<br>(Foveros, etc)                                               |                                                                                                          |                                                                                                                               | Mold<br>compound pop<br>corn;<br>Anisotropic<br>conductive<br>adhesive cracks |                                                                                               | Mold compound pop-coming                                                                                |                                                                                                                     | FinFET ion shift (due to TSV/SI CTE<br>mismatch, µBump stress, shrinkage<br>of underfill & EMC); TSV effects on<br>BTU/HC; BEOL cracking Cu pillar<br>joint fellum; Mold compound pop-<br>corn; conductive adhesive cracking |                                                                                                                                 |                                                                                 |                                                                                                                                       |                                                                    |                                                                                                        |                                                                                                                        |                                                                                                     |                                                                                                                                    |                              |                                            |

|                     |                |                           | Chiplet/KGD                                                                | ESD                                                                                                      |                                                                                                                               |                                                                               |                                                                                               |                                                                                                         |                                                                                                                     | Die edge cracking: Under bump ELK<br>cracking                                                                                                                                                                                |                                                                                                                                 |                                                                                 |                                                                                                                                       |                                                                    |                                                                                                        |                                                                                                                        |                                                                                                     |                                                                                                                                    |                              |                                            |

| N                   | /lodule/System | Module/ System            | Printed Circuit<br>Board Assembly                                          | Leakage current<br>and shorts from<br>Conductive<br>filament<br>formation                                | electro-chemical metal<br>migration                                                                                           | PCB Board<br>electrical<br>model                                              | \Co-thermal sim<br>from die to package<br>to system                                           | leakage current and<br>shorts from loss of<br>surface insulation<br>resistance &<br>conductive filament | moisture ingress,<br>leading to fiber-<br>matrix debonding,<br>and electro-chemical<br>metal migration              | Solder joint cracking; Cracking of<br>PTH plating; PCB delamination;<br>trace cracking; Warpage                                                                                                                              | thermomechanical fatigue<br>of trace and solder, IMC<br>fracture; CTE mismatches<br>between: component /<br>PWS. metallization/ | Solder joint<br>cracking: pad<br>cratering                                      | Stress exceeds the material and interface strength                                                                                    | Effects of PCB<br>temp and<br>corrosion on<br>electrical<br>model? | Effects of PCB<br>stress on<br>electrical<br>model?                                                    | Board level Solder<br>Joint Reliability                                                                                | ANSYS Mechanical                                                                                    | PCB thermal/ mechanical<br>properties; Solder joint<br>fatigue/creep model;<br>Solder joint dyannic/<br>properties                 |                              |                                            |

#### **Thank You**