### IEEE **ELECTRONICS PACKAGING SOCIETY** Newsletter

**JULY 2018** VOL. 40 NO. 2 ISSN 1077-2999

**Driving Innovation in Microsystem Packaging**

/// **EPS.IEEE.ORG**

#### PRESIDENT'S COLUMN

Avram Bar-Cohen. PhD, Principal Engineering Fellow, Raytheon—Space and Airborne Systems, Arlington, VA

ear Colleagues, friends, and members of the Electronic Packaging community:

I am just back from San Diego and still basking in the glow of our most successful ECTC Conference ever. This Conference, as the electronic packaging community we serve, has grown enormously in size and in impact since its inception in 1950 in Washington DC as the "Symposium of Improved Quality Electronic Components." The success of that Symposium resulted in a second symposium in 1952 and annual meetings for the subsequent 66 years; since 1962 with joint sponsorship by IEEE and EIA,

and solely under our auspices for the past 7 years. The approximately 1750 participants in this year's ECTC, along with nearly 400 in the co-located thermal-packaging ITHERM Conference, constituted the largest gathering of Packaging professionals in the history of our Society, totaling almost 2500 attendees. The two Conferences also provided us all with the opportunity to meet and help recognize, through the EPS, ECTC, and ITHERM awards, some of the incredible engineers and scientists who have made Packaging what it is today.

I would like to take this opportunity to thank the ECTC Executive and Program Committees, the ITHERM Executive and Program Committees, the Board of Governors and members of the EPS Society, who along with the ECTC, ITHERM, and EPS staff, have made this the premier annual event of the electronic packaging community. We are fortunate to have so many of you actively engaged in these two Conferences and we are indebted to the large, highly-skilled, and enthusiastic team that keeps finding new ways to enhance and better integrate these Conferences.

The ECTC/ITHERM attendees and the nearly 3000 additional participants in our flagship Asia-Pacific Conference (EPTC), our flagship European Conference (ESTC), and the other EPS sponsored and co-sponsored Conferences, as well as the 10's of thousands who regularly download EPS papers thru Xplore, have helped to establish the broad, international footprint of this Electronics Packaging Society. Together we are heirs to a rich history

of leading and giving witness to successive revolutions in component and packaging technology.

There has never been a time in our history when Packaging Science and Technology was more prominent or better positioned for future impact on our community. As we well know, the current wave of expansion and change in the electronics industry has identified electronic packaging as a cutting-edge value creator and product differentiator. With growing frequency, packaging is driving change in the microelectronic industry, building on innovations in 2.5D and 3D packaging, compound semiconductor materials, and heterogeneous integration to lay the groundwork for the approaching inflection in IoT technology, a new 5G generation of telecommunication hardware, and the introduction of new computational modalities, from quantum to neuromorphic computing.

As you have heard—or read—me say before, I believe that our new name—the Electronics Packaging Society—and the changed dynamics of the electronic industry provide us with a unique opportunity to:

- Take ownership of, i.e. Brand, Packaging and Interconnection across all scales and applications;

- Drive industry recognition for the strategic value of packaging, and

- Become the premier source—within IEEE and the broader community-of packaging and integration knowledge and expertise.

But we cannot succeed in realizing this EPS Vision without your engagement and commitment. As members of IEEE and

(continued on page 9)

#### **NEWSLETTER SUBMISSION DEADLINES**

1 December 2018 for Winter issue 2019 15 June 2019 for Summer issue 2019

Submit all material to d.manning@ieee.org

#### **EPS Officers**

President: Avram Bar-Cohen avram bar-cohen

@raytheon.com patrick.thompson@ti.com

VP (Technology): Patrick Thompson **VP** (Conferences): Chris Bailey c.bailey@gre.ac.uk **VP** (Publications): Ravi Mahajan ravi.v.mahajan@intel.com **VP** (Education): Beth Keser beth.keser@intel.com **VP** (Finance):

Thomas Reynolds t.reynolds@ieee.org Sr. Past Pres.: Jean Trewhella iean.trewhella@GLOBAL

FOUNDRIES.com Ir. Past Pres.: jixue@cisco.com

**Members At Large**

2018 Term End: Regions 1-6, 7, 9—Philip Garrou, Eric Perfecto; Region 8—

Karlheinz Bock; Region 10—C. Robert Kao, Andrew Tay,

Suresh Subramanyam

2019 Term End: Regions 1-6, 7, 9-Li Li, David McCann, Kitty Pearsall,

Subramanian S. Iyer; Region 8—Thomas Brunschwiler,

Gilles Poupon

2020 Term End: Regions 1-6, 7, 9-Alan Huffman, Sam Karikalan,

Xuejun Fan, Jeff Suhling; Region 8-Grace O'Malley;

Region 10-Yoichi Taira

#### **Publications**

Transactions on Components, Packaging and Manufacturing Technology

**Managing Editor:**

Ravi Mahajan

Senior Area Editor, Special Topics:

Ravi Mahajan

Senior Area Editor, Electrical Performance:

Dale Becker

Senior Area Editor, Components: Characterization and Modeling:

Koneru Ramakrishna

Senior Area Editor, Advanced Packaging Technologies:

Kuo-Ning Chiang

Senior Area Editor, Electronics Manufacturing:

Muhannid Bakir

#### **Technical Committee Chairs**

**Materials & Processes:**

Myung Jin Yim

**High Density Substrates & Boards:**

Yasumitsu Orii

Electrical Design, Modeling & Simulation:

Dale Becker

Thermal & Mechanical:

Dereje Agonafer

**Emerging Technology:**

Karlheinz Bock

Nanotechnology:

Americas: Raj M. Pulugurtha, Chair; Europe: Chris Bailey,

Asia:Katsuaki Suganuma

Power & Energy:

Patrick McCluskey

RF & Thz Technologies:

Manos Tentzeris

Green Electronics:

Nils F. Nissen

Photonics—Communication, Sensing, Lighting:

Gnyaneshwar Ramakrishna,

3D/TSV:

Paul Franzon

Reliability:

Richard Rac

#### **Program Directors**

Membership Programs: Jeffrey C. Suhling, jsuhling@auburn.edu Chapter Programs: Kitty Pearsall, kitty.pearsall@gmail.com

Awards Programs: Eric Perfecto, eric.perfecto@globalfoundries.com

Student Programs: Andrew Tay, andrew\_tay@ieee.org

Industry Programs: William T. Chen, William.Chen@aseus.com Region 8 Programs: Toni Mattila, toni.mattila@investinfinland.fi Region 10 Programs: Yasumitsu Orii, yasumitsu.orii@nagase.co.jp

#### **Standing Committee Chairs**

Fellows Evaluation: CP Wong, cp.wong@ieee.org

Long Range / Strategic Planning: Jie Xue, jixue@cisco.com

Nominations: Jean Trewhella Jean. Trewhella@ globalfoundries.com

#### **Distinguished Lecturers**

Program Director: Beth Keser, beth.keser@intel.com

Lecturers: Mudasir Ahmad, Muhannad Bakir, Ph.D., Avram Bar-Cohen, Ph.D., Karlheinz Bock, Ph.D., Bill Bottoms, Ph.D., Chris Bower, Ph.D., Moises Cases, William T. Chen, Ph.D., Xuejun Fan, Ph.D., Paul D. Franzon, Ph.D., Philip Garrou, Ph.D., R. Wayne Johnson, Ph.D., Beth Keser, Ph.D., John H. Lau, Ph.D., Ning-Cheng Lee, Ph.D., S. W. Ricky Lee, Ph.D., Johan Liu, Ph.D., Ravi Mahajan, PhD., James E. Morris, Ph.D., Kyung W. Paik, Ph.D., Mervi Paulasto-Kröckel, Ph.D., Michael Pecht, Ph.D., Eric D. Perfecto, Karl J. Puttlitz, Ph.D., Dongkai Shangguan, Ph.D., Nihal Sinnadurai, Ph.D., Ephraim Suhir, Ph.D., Rao Tummala, Ph.D., Walter Trybula, Ph.D., E. Jan Vardaman, Paul Wesling, CP Wong, Ph.D., Jie Xue, Ph.D., Kishio Yokouchi, Ph.D.

#### **Chapters and Student Branch Chapters**

Refer to eps.ieee.org for EP Society Chapters and Student Branch Chapters list

IEEE Electronics Packaging Society Newsletter is published quarterly by the Electronics Packaging Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016-5997. US \$1.00 per member per year is included in Society fee for each member of the Electronics Packaging Society. Printed in U.S.A. Periodicals postage paid at New York, NY, and at additional mailing offices. Postmaster: Send address changes to IEEE EPS Newsletter, IEEE 445 Hoes Lane, Piscataway, NJ 08854. All rights reserved, copyright (c) 2018 by the EP Society of IEEE. Authors and Artists given full permission for further use of their contributions. For circulation information call IEEE Customer Service 800-701-4333, or FAX 908-981-9667.

#### Circulate your printed or PDF copy of this **NEWSLETTER** to co-workers.

IEEE prohibits discrimination, harassment, and bullying For more information, visit http://www.ieee.org/web/aboutus/ whatis/policies/p9-26.html

SFI Logo

#### **EPS NEWS**

#### The Next Phase of Innovation: Heterogeneous Integration

e are entering the era of digital economy and myriad connectivity. Look around you: the migration of data to the cloud, presence of smart devices everywhere and the emergence of autonomous vehicles are all great examples.

Recently, artificial intelligence and big data analytics have been undergirding the technical advances in every market. At this inflexion point, though, with the plateauing of semiconductor scaling and the explosive expansion of electronic products into global society, continued technological progress will require a new phase of electronics innovations.

Heterogeneous integration is rapidly becoming the key technology for the next decade, and will initiate a new era of technological and scientific advances. Heterogeneous integration refers to the integration of separately-manufactured components into a higher-level assembly that, in total, provides enhanced functionality and improved operating characteristics.

Packaging, for both systems and devices, will be the vanguard to this enormous advance. As a result, heterogeneous integration has become the highest strategic initiative of the IEEE Electronics Packaging Society (EPS), from conferences, publications, education, technology, and industry outreach.

Heterogeneous Integration Roadmap (HIR), initiated by EPS is now sponsored by three IEEE Societies together with ASME EPPD and SEMI, is at the forefront of this strategic initiative. Our vision is to colloaborate with organizations with likeminded vision and open governance.

The mission of the Heterogeneous Integration Roadmap is to provide guidance to the profession, industry, academia and government on key technical challenges with sufficient lead time to prevent them from becoming roadblocks to continued progress in electronics. That progress is essential to the future growth of the industry, and to the realization of technology's promise of continued positive impact on mankind.

We would like to invite the readers to access the Heterogeneous Integration Roadmap page in the EPS Website under Technology under the link: http://eps.ieee.org/technology/heterogeneous-integration-roadmap.html

The readers will find information on

- Background

- Global Advisory Council

- Mission

- Scope

- Purpose

- Technical Working Groups

- Committee

Global Events

We had a very successful 1st Heterogeneous Integration Roadmap (HIR) Symposium in Santa Clara sponsored by the EPS Santa Clara Chapter. This was followed by HIR Workshop at ECTC-ITHERM Conferences in San Diego May 29th. This month in July we shall have work session at SEMICON West in San Francisco. These face to face work sessions together with weekly conference calls is designed to bring us to publication of the 1st edition of the Heterogeneous Integration Roadmap in September, We believe that with the rapid and disrutive changes in our industry, annual revision will be in order. This will be our goal.

Contributor: William Chen IEEE Fellow

### 2018 IEEE Electronics Packaging Society Award Recipients

#### William T. Chen

An IEEE Fellow, ASE Fellow and senior technical advisor with ASE Group, Inc., Sunnyvale, CA

#### 2018 IEEE Electronics Packaging Award

For contributions to electronic packaging from research and development through industrialization, and for his leadership in strategic roadmapping efforts.

*Note:* "Please read a Q&A with Bill Chen later in the newsletter" IEEE grade to award winners:

- Douglas Yu: IEEE Fellow

- Pradeep Lall: IEEE Fellow

- Muhannad Bakir: IEEE Senior Member

- Kuan-Neng Chen: IEEE Fellow

- Katsuyuki Sakuma: IEEE Senior Member

- Jean Trewhella: IEEE Senior Member

### Company, Taiwan

### 2018 IEEE CPMT Electronics Manufacturing Technology Award

For contributions to the development and high-volume manufacturing of Interposers and Wafer-Level Fan-Out Packaging.

**Pradeep Lall, IEEE Fellow** Auburn University, USA

### 2018 IEEE CPMT Outstanding Sustained Technical Contribution Award

For outstanding sustained contributions to the design, reliability and prognostics for harsh environment electronics systems.

Annette Teng, IEEE Senior Member Promex Industries Inc., USA

2018 IEEE EPS Regional Contributions Award—Region 1-6, 7 & 9 (Americas) For sustained contributions to the Santa Clara Valley Chapter and continued support of Chapter activities.

**Kuan-Neng Chen, IEEE Fellow** National Chiao Tung University, Taiwan

**Katsuyuki Sakuma, IEEE Senior Member** IBM T.J. Watson Research Center, USA

**2018 IEEE EPS Exceptional Technical Achievement Award**For contributions to 2.5D and 3D IC heterogeneous integration, with focus on interconnect technologies.

Jean Trewhella, IEEE Senior Member GLOBALFOUNDRIES, USA

2018 IEEE EPS David Feldman Outstanding Contribution Award

For 20 years of leadership consistently driving change, collaboration, and engagement in EPS and ECTC, including driving our society name change, sponsoring the

Heterogeneous Integration Roadmap, and establishing the ECTC Student Reception.

**Gilles Poupon, IEEE Senior Member** CEA-LETI, France

#### 2018 IEEE EPS Regional Contributions Award—Region 8 (Europe, Middle East, Africa)

For outstanding and sustained contributions and leadership in regional activities such as organization of international con-

ferences and workshops, active volunteering in technical committees, and leading the EPS French chapter to one of the most active chapters in the region.

Yoshitaka Fukuoka, IEEE Fellow Worldwide Electronic Integrated Substrate Technology Inc., Japan

#### 2018 IEEE EPS Regional Contributions Award—Region 10 (Asia and Pacific) For contributions to establish an International

Japanese conference on electronic packaging and to provide the latest packaging technology

information in Japan to the world.

#### **Congratulations to IEEE EPS Senior Members**

#### **New IEEE EPS Senior Members**

The members listed below were elevated to the grade of Senior Member between December 2017 and April 2018.

The grade of Senior Member is the highest for which application may be made and shall require experience reflecting professional maturity. For admission or transfer to the grade of Senior Member, a candidate shall be an engineer, scientist, educator, technical executive, or originator in IEEE designated fields for a total of 10 years and have demonstrated 5 years of significant performance.

Individuals may apply for Senior Member grade online at: https://www.ieee.org/membership/senior/application/index.html

Ian Harvey Arellano, Republic of Philippines Section Hidetaka Hayashi, Tokyo Section

Randy Crutchfield, Phoenix Section Shaowu Huang, Santa Clara Valley Section

#### **ECTC 2018 Travel Award Winners**

Congratulations to the winners of the 2018 ECTC travel award. The award is intended to assist students to attend ECTC.

- Luca Del Carro, ETH Zurich

- Normand-Pierre Goodhue, Université de Sherbrooke

- Siva Chandra Jangam, University of California, Los Angeles

- Chenhui Li, Eindhoven University of Technology

- Tong-Hong Lin, Georgia Institute of Technology

- Nivesh Mangal, Ghent University

- Saikat Mondal, Michigan State University

- **Bo Song**, Georgia Institute of Technology

#### **Congratulations to the ECTC Volunteer Award Recipients**

The EPS/ECTC Volunteer Award is given to those individuals who contribute to the success of the ECTC by volunteering in one of the conference committees, year after year. Here are the 2018 EPS/ECTC Volunteer Award winners:

| Rozalia Beica  | 10 Years |

|----------------|----------|

| Karlheinz Bock | 10 Years |

| Zhaoqing Chen  | 10 Years |

| Vijay Khanna   | 10 Years |

| James Lu     | 10 Years |

|--------------|----------|

| Mikel Miller | 10 Years |

| Shichun Qu   | 10 Years |

| Sandeep Sane | 10 Years |

| Matthew Yao     | 10 Years |

|-----------------|----------|

| Tieyu Zheng     | 10 Years |

| Thomas Reynolds | 25 Years |

#### EPS Major Awards Nomination Period Starts on September 15

or the first time all the EPS Major Award nominations will require line submission. The nomination period to input all the required documents runs from September 15 to January 21. The Electronics Packaging Society offers the following awards for the purpose of recognizing outstanding service and contributions to furthering the professional purposes of IEEE and EP Society.

#### **Outstanding Sustained Technical Contributions Award**

To recognize outstanding sustained and continuing contributions to the technology in fields encompassed by the EP Society.

Prize: \$3,000 and Certificate

**Basis for Judging**: Technical contributions must be sustained and continuing over a period of at least 15 and preferably 20 years. One major contribution will not qualify. Must be documented by open literature publications such as papers, patents, books and reports (available to the public).

**Eligibility**: Must have been a member of the IEEE and EP Society for the past three (3) years (2016-2018), and renewed for 2019.

#### **Electronics Manufacturing Technology Award**

To recognize major contributions to Electronic Manufacturing Technology in fields encompassed by the EP Society.

Prize: \$3,000 and Certificate

Basis for Judging: Contributions may include technical development of, or management (directing) of major new electronic manufacturing processes; significantly increasing yield and/or reliability of established manufacturing processes, etc. Contributions must be sustained and continuing over a period of at least 15 and preferably 20 years. Work in the management of EPS Conferences or its BoG may be contributory but it is not a requirement for the award.

Eligibility: No need to be a member of IEEE and EP Society.

#### **David Feldman Outstanding Contribution Award**

To recognize outstanding contributions to the fields encompassed by the EP Society through executive or managerial directions.

**Prize**: \$2,500 and Certificate

Basis for Judging: Contributions to the organizations or enterprises connected with the field; contributions to EPS Chapter or Board of Governors activities; contributions to the fields encompassed by the EP Society.

Eligibility: Recipient must have been a member of IEEE and EPS for the past five (5) years (2014-2018), and renewed for 2019.

#### **Exceptional Technical Achievement Award**

To recognize an individual, or group of individuals (no more than three), for exceptional technical achievement in the fields encompassed by the EP Society.

Prize: \$2,500 and a Certificate.

Basis for Judging: Technical contributions of the nominee(s) must be such that they are considered to be exceptional, not achieved by most members. A single major contribution will qualify for this award. The contribution could be a significant invention, introduction of a significantly new and important technology or product (in which case, the nominee may be a team leader), or significant work that advances the state-of-the-art in EPS's field of interest. The technical contributions must be documented by open literature publications such as papers, patents, books, and reports (available to the public). Technical recognition and awards from the organization employing the individual as well as awards from other IEEE and non-IEEE technical societies may also be contributory.

**Eligibility**: Recipient(s) must have been a member of IEEE and EPS for the past three (3) years (2016–2018), and renewed for 2019. There are no requirements for service to the IEEE or EP Society.

#### **Outstanding Young Engineer Award**

To recognize outstanding contributions to the fields encompassed by the EP Society through invention, technical development, publications, or new product implementation.

Prize: \$1,500 and Certificate

Basis for Judging: Technical contributions through patent invention, contributions to technology or product development within the EPS Field of Interest. May encompass management (directing) of significant new product introduction or implementation of major new electronic manufacturing processes; significantly increasing yield and/or reliability of established manufacturing processes. Contributions to the Society, through the BoG, Conferences, Chapters, etc., will also be considered. Proof of contributions may consist of open literature publications (preferred) such as papers, patents, books, and reports (available to the public). At least three (3) letters from peers and management at the nominee's place of

employment attesting to the accomplishment(s) can be accepted in lieu of publications.

**Eligibility**: Must have been a member of the IEEE and EPS (member grade or above) for the past three (3) years (2016–2018), and renewed for 2019, and must be 35 years of age, or younger, on December 31, 2018.

#### **Guidelines for Nominators:**

- A recipient of any EPS Major Award will be eligible for nomination for another EPS Major Award after two award cycles have passed. (i.e., Recipient of XX Award in 2016 becomes eligible for nomination for YY Award in 2019). For lists of past awardees, see http://eps.ieee.org/awards.html

- Past recipients of an award are not eligible to receive that same award. For lists of past awardees, see http://eps.ieee.org/awards.html

- An individual may submit only one nomination per award but may submit nominations for more than one award.

- An individual may submit only one endorsement per award but may submit endorsement for more than one award.

- It is the responsibility of the nominator to ensure quality documentation to assist the Awards Committee in evaluating the candidate.

- Outstanding Sustained Technical Contribution Award is designed for the "practitioner", while the Electronics Manufacturing Technology Award intended for "Corporate Leadership".

- Complimentary material, such as candidates picture, CV, list

of publications and/or patents should be submitted separate from

the award nomination.

- Self-nominations will **not** be considered.

- All nominations must be online. Nominations questions can be send to Society Awards Program director:

#### **Eric Perfecto**

GLOBALFOUNDRIES 2070 Route 52 MS: 6C1 Hopewell Junction, NY 12533 eric.perfecto@globalfoundries.com ph: 845-894-4400

Winners will be notified by 9 April 2019, and the awards will be presented at the 69th Electronic Components and Technology Conference (ECTC), May 28–31, 2019 at the The Cosmopolitan of Las Vegas, Las Vegas, NV (USA).

### Functional Teams—Rationale, Activities, and Future Plans

arly in 2018 the EPS Board of Governors established several Functional Teams to broaden the interaction between Officers ■ and Members-at-Large around key issues for the Society and to nucleate and develop new initiatives that would provide added-value to EPS members and the community. Four Functional Teams were assembled: Conferences and Education – led jointly by Chis Bailey, VP of Conferences, and Beth Keser, VP of Education; Membership—led by Jeff Suhling, Director of Membership Programs, and Technology led by Patrick Thompson, VP of Technology, as well as a small **Finance** Functional Team, led by Tom Reynolds, VP of Finance. The full membership of each Functional Team, including several EPS Directors and Members-at-Large, is listed below. It is anticipated that some Functional Teams will be retired, once their mission is completed, and that other Functional Teams will be created as needed to address emerging challenges and opportunities. We invite your comments on any and all of the activities of these Functional Teams and would very much welcome additional participants from among the EPS members in any of the FT's. Please write to Avi Bar-Cohen or Denise Manning to provide your feedback or volunteer for one of the Functional Teams.

#### **Conference/Education Functional Team:**

Due to the high connectivity of EPS conference and educational activities, as well as the principals' interest in both domains, it was decided to create a single, combined Functional Team for Conferences and Education. This Functional Team has pursued two primary initiatives:

#### 1) Electronic Packaging Conference Asia Pacific (EPCAP)

EPS currently co-sponsors 8 separate events in the Asia-Pacific region, R10, with a total of approximately 700 attendees in the Financially-(co-)Sponsored Conferences and a similar number for the Technically-(co-)Sponsored conferences. The FT is exploring whether a larger, 1,000+ attendees, annual, fully-sponsored EPS Conference, building on the "best practices" established by ECTC, would better "brand" EPS and more effectively serve our members and the Packaging community in Region 10. The current discussion envisions building on and regionalizing EPTC—the EPS flagship Conference—and like ECTC, have it rotate across 3-4 R10 cities, include 50+ exhibits and sponsorships, provide broad topical coverage across all domains of Packaging, with special emphasis on emerging technologies. Moreover, it is hoped that the additional resources generated by such an EPCAP could be used to support Workshops and educational activities in the narrower topical areas covered by ICSJ, EDAPS, EMAPS, and IEMT, as well as new emerging areas, including 5G, "digital manufacturing," and Quantum, as well as Neuromorphic Computing.

#### 2) EPS Proficiency Program

In addition to Continuing Education Units (CEU) and Professional Development Hours (PDH) for the EPS Professional Development Courses at our flagship Conferences, we are now offering PDHs for our webinars. The PDCs and webinars are growing in popularity and IEEE-wide surveys with non-members, especially Young Professionals, have identified a strong interest in additional "credentialing," at intermediate levels between Member/Senior Member

and Fellow. The Conference/Education FT is exploring the possibility of developing an EPS Proficiency Program that would recognize a participant's completion of a set number of the available PDCs and webinars, as well as "softer" skill IEEE webinars, with an EPS Proficiency certificate. Higher levels of Proficiency could also be recognized with higher-level certificates.

#### **Membership Functional Team**

Membership growth, especially in the Young Professional category, is a critical requirement for the future viability of EPS. The membership Functional Team is addressing 3 distinct areas of membership development: Student Members, Young Professionals, and new Chapter formation. In the Student category, the FT has recommended that students attending ECTC and/or ITHERM receive a "free" half-year membership in IEEE/EPS. Effort is also being devoted to reinvigorating existing Student Branch Chapters and developing new Student Branch Chapters on campuses with active electronic packaging programs. Other ideas under consideration, include: collecting student resumes and holding Job Fairs at EPS Conferences, adding Electronic Bulletin Board on the EPS website for packaging position announcements, developing a pool of EPS Mentors, made available through the EPS Website and Collabratec, and updating the list of Universities doing Packaging research.

EPS has appointed Yan Liu as its representative to the IEEE Young Professional Council and also to a 1-year term on the EPS BOG. Dr. Liu is recruiting an EPS YP Committee that will recommend a range of YP activities to the BOG.

The Membership FT is helping to develop a new SE New York Chapter and analyzing membership statistics to identify areas of membership concentration that could benefit from a local Section.

#### **Technology Functional Team**

The Technology FT has been examining ways to reinvigorate the EPS Technical Committees, with special emphasis on the Emerging Technologies Committee that plays a critical role in maintaining EPS' presence on the cutting edge of packaging technology. Under the guidance of Karlheinz Bock, the newly appointed Chair of the Emerging Technologies committee, is exploring the best ways to announce and manage a pilot White Paper competition on visions of "Packaging 2025," focused primarily on Young Professionals and Graduate students. It is expected that the Committee will solicit, review, and rank White Paper contributions from EPS members and invite the top teams to present their Vision(s) to the BOG, and—perhaps—attendees—at ECTC.

The FT is also seeking to play a role in coordinating and scheduling EPS Webinars with the VP-Education and look for other collaboration opportunities with the VP-Education and VP-Conferences. Identifying EPS representatives to IEEE-wide Councils and Working Groups remains a challenge and concern for this functional team.

#### **Finance Functional Team**

The Finance FT is engaged in reviewing and implementing IEEE-wide efforts to bring greater clarity and transparency to the budgeting and indirect/direct charging process. It is also helping to define the best ways to fund projects and initiatives that increase and improve the services and benefits to EPS members.

#### **Conference/Education Functional Team**

- Chris Bailey, EPS VP-Conference

- Beth Keser, EPS VP-Education

- Avi Bar-Cohen, EPS President

- Xuejun Fan, EPS Member at Large

- Alan Huffman, EPS Member at Large

- Grace O'Malley, EPS Member at Large

- Yasumitsu Orii, EPS Program Director Region 10

- Andrew Tay, EPS Program Director Student Programs

#### **Membership Functional Team**

- Jeff Suhling, EPS Program Director Membership Programs

- Kitty Pearsall, EPS Program Director Chapter Programs

- Andrew Tay, EPS Program Director Student Programs

- Avi Bar-Cohen, EPS President

- Jie Xue, EPS Senior Past President

- Pat Thompson, EPS VP-Technology

- Grace O'Malley, EPS Member at Large

- C. Robert Kao, EPS Member at Large

- Sam Karikalan, EPS Member at Large

- Eric Perfecto, EPS Program Director Awards Programs

- Alan Huffman, EPS Member at Large

- Yoichi Taira, EPS Member at Large

- Yan Liu, EPS Young Professional Representative

#### **Technology Functional Team**

- Pat Thompson, EPS VP-Technology

- Avi Bar-Cohen, EPS President

- Bill Chen, EPS Program Director Industry Programs

- Eric Perfecto, EPS Program Director Awards Programs

- Dave McCann, EPS Member at Large

- Raj Pulugurtha, EPS Technical Committee Chair

#### **Finance Functional Team**

- · Pat Thompson, EPS VP-Technology

- Tom Reynolds, EPS VP-Finance

- Avi Bar-Cohen, EPS President

If you are interested in participating in one of the Functional Teams or having any comments for the teams, please send to Denise Manning (d.manning@ieee.org) or Avi Bar-Cohen (Avram.Bar-Cohen@raytheon.com).

#### **Young Professionals Event**

he IEEE Young Professional and Graduate Student Survey in 2016 showed that networking and education are top improvement opportunities among Young Professionals—likely due to being in the early stages of their career. There is significant room for satisfaction improvement in career services as well. Based on the survey results, EPS focuses on improving networking opportunity and providing more career services to YP members this year.

EPS is planning different types of YP meet up events like panel discussion, seminars, and receptions in conferences as well as local sessions. Recently, the 1st ECTC/ITherm Young Professionals Panel Discussion and Reception took place at San Diego on May 29, 2018. Yan Liu, the Electronic Packaging Society Young Professional representative hosted this event. There were 80 attendees joined this event, including ECTC/Therm young professional registrants and IEEE San Diego session young professionals. Two panelists Steve Bezuk (a senior director from Qualcomm Technologies Inc.) and Dr. Kathleen Kramer (IEEE Region 6 director and a professor from University of San Diego) shared their career development advices for young professionals based on their experiences and achievements in industry and academia. This event was very

informative and well received. We would like to thank the funding support from IEEE Young Professional, as well as the great support from ECTC/ITherm and IEEE San Diego session.

In addition, EPS monthly eNews covers more resources for YPs, e.g. Webinars, short courses, upcoming conferences, most popular CPMT papers, and career services. Take career services for example, EPS provides new "Career" section on EPS website, including access to latest job listing on IEEE jobsite, access to IEEE Resume Lab, and access to IEEE Mentoring Program where EPS senior members registered as mentors.

EPS YP group also actively involves in IEEE YP activities. The IEEE YP rep groups have regular monthly conference calls to share the local YP events/activities with each other. This year, the IEEE YP Summit took place in Orlando Feb. 2018. The twenty-five YP representatives from different IEEE regions/sections/societies including EPS joined the inspiring meeting. Team discussed about skill gaps, diversity and inclusion, and career development for young professionals. They also brainstormed and shared the keys and strategies to engage young professionals, to benefit the YP initiatives in different regions/sections/societies.

Yan Liu IEEE EPS Young Professional Representative

#### PUBLICATION NEWS

#### **2017 CPMT Best Transactions Paper Awards**

ach year, the Editors of the IEEE Transactions on Components, Packaging and Manufacturing Technology select the best papers published in the prior year. The papers are selected from among over 200 published papers and represent the best, based on criteria including originality, significance, completeness and organization. The awards were presented at the 68th Electronic Components and Technology Conference (ECTC), June 2018.

Subscribers to this publication can access the papers on-line in IEEE Xplore at:

http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=5503870

#### **Components: Characterization and Modeling Category**

"Monolithic Integration of a Micropin-fin Heat Sink in a 28 nm FPGA"

VOL. 7, ISSUE 10, OCTOBER 2017

Thomas Sarvey, Yang Zhang, Colman Cheung, Ravi Gutala, Arifur Rahman, Aravind Dasu, Muhannad S. Bakir

**Abstract:** Microfluidic cooling has been demonstrated as an effective means of cooling microelectronic circuits with a very low convective thermal resistance and potential for integration in close proximity to the area of heat generation. However, microfluidic cooling experiments to date have been limited to silicon with resistive heaters representing the heat generating circuitry. In this paper, a micropin-fin heat sink is etched into the back side of an Altera Stratix V field-programmable gate array (FPGA), built in a 28-nm CMOS process. Thermal and electrical measurements are made running a benchmark pulse compression algorithm on the FPGA. Deionized water is used as a coolant with flow rates ranging from 0.15 to 3.0 mL/s and inlet temperature ranging from 21 °C to 50 °C. An average junction-to-inlet thermal resistance of 0.07 °C/W is achieved.

URL: https://ieeexplore.ieee.org/document/8038817/

#### **Electrical Performance of Integrated Systems Category**

"Big-Data Tensor Recovery for High-Dimensional Uncertainty Quantification of Process Variations"

VOL. 7, ISSUE 5, MAY 2017

Zheng Zhang, Tsui-Wei Weng, Luca Daniel

**Abstract:** Fabrication process variations are a major source of yield degradation in the nanoscale design of integrated circuits (ICs), microelectromechanical systems (MEMSs), and photonic circuits. Stochastic spectral methods are a promising technique to quantify the uncertainties caused by process variations. Despite their superior efficiency over Monte Carlo for many design cases, stochastic spectral methods suffer from the curse of dimensionality, i.e., their computational cost grows very fast as the number of random parameters increases. In order to solve this challenging problem, this paper presents a high-dimensional uncertainty quantification algorithm from a big data perspective. Specifically, we show that the huge number of (e.g.,  $1.5 \times 10^{27}$ ) simulation samples in standard stochastic collocation can be reduced to a very small one (e.g., 500) by exploiting some hidden structures of a high-dimensional data array. This idea is formulated as a tensor recovery problem with sparse and low-rank constraints, and it is solved with an alternating minimization approach. The numerical results show that our approach can efficiently simulate some IC, MEMS, and photonic problems with over 50 independent random parameters, whereas the traditional algorithm can only deal with a small number of random parameters.

URL: https://ieeexplore.ieee.org/document/7775008/

#### AND

"High-Fidelity, High-Performance Computational Algorithms for Intra-System Electromagnetic Interference Analysis of IC and Electronics"

VOL. 7, ISSUE 5, MAY 2017

Zhen Peng, Yang Shao, Hong-Wei Gao, Shu Wang, Shen Lin

Abstract: Ever-increasing complexity in high-speed electronic devices and systems presents significant computational challenges in the numerical analysis in terms of desired accuracy, efficiency, and scalable parallelism. The objective of this paper is to investigate high-resolution, high-performance full-wave field solvers for scalable electromagnetic simulations of product-level integrated circuits (ICs) and electronics. The emphasis is placed on advancing parallel algorithms that are provably scalable facilitating a design-through-analysis paradigm, and enabling concurrent multiscale modeling and computation. The capability and the benefits of the algorithms are validated and illustrated through complex 3-D IC and electronics applications.

URL: https://ieeexplore.ieee.org/document/7817743/

#### 5 Most Popular Articles According to May 2018 Usage Statistics

### Manufacturing Considerations in the 3-D Printing of Fractal Antennas

Sung Yun Jun; Benito Sanz-Izquierdo; Edward A. Parker; David

Bird; Alan McClelland

Publication Year: 2017, Page(s): 1891-1898

#### 3-D Printed Metal-Pipe Rectangular Waveguides

Mario D'Auria; William J. Otter; Jonathan Hazell; Brendan T. W. Gillatt; Callum Long-Collins; Nick M. Ridler; Stepan Lucyszyn

Publication Year: 2015, Page(s): 1339-1349

### **Expected Failures in 3-D Technology and Related Failure Analysis Challenges**

Ingrid De Wolf; Kristof Croes; Eric Beyne Publication Year: 2018, Page(s): 711–718

#### **Managing Electronics Part Changes in the Supply Chain**

Michael Pecht; François Dagorn; Diganta Das Publication Year: 2018, Page(s): 883–895

A Filtering Dual-Polarized Antenna Subarray Targeting for Base Stations in Millimeter-Wave 5G Wireless Communications

Hui Chu; Yong-Xin Guo

Publication Year: 2017, Page(s): 964–973

#### **President's Column** (Continued from page 1)

EPS you already enjoy the highest quality technical Conferences, Workshops, and Seminars in the business, as well as discounts on Conferences, free Webinars, low-price online subscriptions to the IEEE Transactions, awards and recognition, and opportunities for professional and personal relationships with your peers at the local level throughout the world. But even more importantly, membership and engagement in EPS puts you in the center of the packaging universe—allowing you to recognize emerging technologies in "real time," to interact with many of the packaging luminaries "up close and personally," to work with your packaging peers to drive the next generations of packaging S&T, and to define and

steer your professional trajectory towards your personal and professional goals.

So, please take this opportunity to contact me directly (avram. bar-cohen@raytheon.com) to express an opinion or raise a question about our activities and to let me know of your interest join or start a new Technical Committee, volunteer to represent EPS on one of the IEEE-wide Initiatives, or to find out how to join our Board of Governors. It is only with all of you that we can successfully usher in the packaging technologies for future product generations and drive innovation in the microelectronic industry.

#### **EDUCATION/CAREER NEWS**

#### **EPS Announces a New PhD Fellowship Award**

he EPS Board of Governors voted unanimously to establish a PhD Fellowship award in the area of electronics packaging. Graduate Students—Here is what you need to know.

#### Description/Objective

To promote, recognize, and support PhD level study and research within the Electronics Packaging Society's field of interest.

#### **Prize**

A plaque and a single annual award of US\$5,000, applicable towards the student's research.

#### **Eligibility**

Candidate must be an IEEE EPS member, at the time of nomination, and be pursuing a doctorate degree within the EPS field of interest on a full-time basis from an accredited graduate school or institution. The candidate must have studied with her/his advisor for at least 1 year, at the time of nomination, to be eligible.

A Student who received a Fellowship award from another IEEE Society, within the same year, or is a previous EPS Fellowship winner is ineligible.

#### **Schedule**

• On-Line application available by September 21

- Complete application packages are due by Jan 15

- Recipients will be notified by Mar 15

- Formal award presentations will take place at the IEEE EPS luncheon at ECTC at end of May.

- Monetary awards will be given by Jun 15 (or at ECTC)

#### Selection/Basis for Judging

Demonstration of his/her significant ability to perform independent research in the fields of electronic packaging and a proven history of academic excellence, as documented in:

- Nomination by an IEEE EPS Member. Only one nomination per member per year.

- Two-page (maximum) statement by the student describing his or her education and

- Research interests, accomplishments, and impact on the electronics package industry.

- Proof of contributions to the community may consist of open literature publications (preferred) such as papers, patents, books, and conference presentations and reports (available to the public).

- At least one letter of recommendation from someone familiar with the student's work

- Student resume

#### **Award Committee**

The committee will consists of the EPS Awards program Director and 4 representatives from industry and academia.

PS Distinguished Lecturers are selected from among EPS Fellows, Award winners, and Society leaders, who are members of the technical community and experts in their field. They are available to present lectures and/or courses at EPS events—Chapters, Conferences, Workshops or Symposia; as well as IEEE Student Chapter events.

The EPS Distinguished Lecturer Program (DLP) aims at serving communities interested in the scientific, engineering, and production aspects of materials, component parts, modules, hybrids and micro-electronic systems for all electronic applications.

The Program strives to support EPS Chapters worldwide by helping them to invite leading researchers in their respective fields and IEEE Student Chapters to encourage students to pursue EPS related fields and to join the EPS society. The DLP talk is a major event in the life of the inviting Chapter.

#### **EPS Distinguished Lecturers**

#### **Mudasir Ahmad**

Cisco Systems, Inc. San Jose, CA USA

**Topics:** Internet of Things (IoT), Advanced Packaging, 2.5D, Heterogeneous Silicon Photonics, Advanced Reliability (Thermo-

mechanical, Mechanical Shock), Numerical Modeling, Advanced Thermal Solutions, Stochastic Analysis, Bayesian Inference, Machine Learning, Artificial Intelligence

#### **Muhannad Bakir**

Georgia Institute of Technology, Atlanta, GA USA

**Topics:** Emerging interconnection architectures and technologies; heterogeneous system design and integration

#### **Avram Bar-Cohen**

University of Maryland, College Park, Maryland USA **Topics:** Thermal packaging

#### Karlheinz Bock

Technische Universität, Dresden, Germany

**Topics:** Multifunctionality & heterosystemintegration & additive manufacturing (IoT, Industry 4.0, tactile internet...), packaging for mechanical, digital and power co-integration (automotive, machines, robots...), 2.5D and 3D electro-optical-RF interposer and board (high performance), heterointegration for flexible, bio, organic and large area electronics (open form factor)

#### **Bill Bottoms**

Third Millennium Test Solutions, Santa Clara, CA USA

**Topics:** Heterogeneous Integration, Semiconductor test technology, Emerging research materials, Packaging of electronic components and systems, the global network and its future requirements, the internet of things and Smart manufacturing

#### **Chris Bower**

X-Celeprint Inc. North Carolina, USA

**Topics:** Novel assembly methods, elastomer stamp micro-transferprinting, heterogeneous integration, three-dimensional integration, manufacturing of micro-assembled displays and other largeformat electronics.

#### **Moises Cases**

The Cases Group, LLC, Austin, Texas, U.S.A.

**Topics:** Signal and power distribution integrity for complex high-speed multiple board system designs; Modeling, simulation and verification of integrated circuits, electronic packages and system interconnect technologies; High-speed and low powers systems interconnect design methodology and tools; Digital system electrical designs, timings and integration; High-speed I/O architectures and designs; Service science management and engineering applied to engineering services

#### William T. Chen, Ph.D. (1/2015–1/2019)

ASE (U.S.) INC

Santa Clara, CA USA

**Topics:** Semiconductor and Electronics Industry Trends and Roadmap

#### Xuejun Fan

Lamar University, Beaumont TX USA

**Topics:** Design, modeling and reliability in micro-/nano- electronic packaging and microsystems

#### Paul D. Franzon

NC State University, Raleigh, NC USA

**Topics:** 3DIC and 3D Packaging Application, Design and CAD; I/O Macromodeling, including IBIS; High-Speed, Low Power Chip to Chip Communications

#### Philip Garrou

Microelectronic Consultants of North Carolina, Research

Triangle Park, NC USA

**Topics:** Thin film technology; IC packaging and interconnect; Microelectronic materials; 3D-IC integration

#### R. Wayne Johnson

Tennessee Tech University, Cookeville, TN USA

**Topics:** Extreme Environment Electronics

#### **Beth Keser**

Intel, Neubiberg, Germany

**Topics:** Fan-Out Wafer Level Packaging and Wafer Level Packaging structures; processes, materials, tools, design rules and roadmaps; photoimageable liquid polymer films

#### John H. Lau

4ASM Pacific Technology, Hong Kong

**Topics:** Electronics and Photonics 2D and 3D packaging and manufacturing

#### Ning-Cheng Lee

Indium Corporation of America, Clinton, NY USA

**Topics:** Lead-free soldering including solderalloys, surface finishes, components, substrates, and other materials; Processes, reliability, failure modes, and troubleshooting; Advanced applications including packaging, and ultra-fine pitch applications

#### S. W. Ricky Lee

Hong Kong University of Science and Technology,

Clear Water Bay, Kowloon, Hong Kong

Topics: Solder Joint Reliability, 3D IC Integration, and LED Packaging

#### Johan Liu

Chalmers University of Technology, Gothenburg, Sweden

Topics: Micro and nano-electronic electrically conductive adhesives

#### Ravi Mahajan

Intel Corporation, Arizona, USA

**Topics:** Advanced Packaging Architectures, Assembly Processes and Thermal Management

#### James E. Morris

Portland State University, Portland, Oregon USA

**Topics:** Electrically conductive adhesives; Electronics packaging; Nanotechnologies

#### Kyung W. Paik

Korea Advanced Institute of Science & Technology,

Daejon, Korea

**Topics:** Electrically conductive adhesives (ACF, NCF, ACP, NC)

#### Mervi Paulasto-Kröckel

Aalto University, Helsinki, Finland

**Topics:** MEMS, electronics reliability, automotive components and packaging, implantable electronics, dissimilar materials & interfaces

#### **Michael Pecht**

University of Maryland, College Park, MD USA

Topics: Prognostics and reliability of electronic products and systems

#### Eric D. Perfecto

GLOBALFOUNDRIES, Hopewell Jct., NY USA

**Topics:** Fine pitch interconnect, chip to chip and chip to laminate connection, UBM and solder selection, chip package interaction and 2.5D fabrication

#### Karl J. Puttlitz

Puttlitz Engineering Consultancy, LLC, Wappingers Falls, NY USA **Topics:** Flip Chip Issues/Technology; Area Array (1st & 2nd Level) Issues/Technology; Lead-free Issues/Technology

#### Dongkai Shangguan

National Center for Advanced Packaging Co., LTD., Wuxi, China **Topics:** Materials, reliability, lead-free, microelectronics packaging, board assembly, electronics manufacturing

#### Nihal Sinnadurai

Suffolk, UK

**Topics:** Accelerated Ageing for Reliability Assurance -theory and practical methods—including HAST (my invention originally); The use of encapsulation and plastic packaging and reliability evaluation method; PCB & Hybrid technologies; Thermal management and design

#### **Ephraim Suhir**

Los Altos, CA USA

**Topics:** Accelerated life testing; Probabilistic physical design for reliability; Bonded assemblies; Thermal stress; Predictive modeling; Fiber optics structures: design for reliability; Dynamic response to shocks and vibrations

#### Rao Tummala

Georgia Institute of Technology, Atlanta, GA USA

**Topics:** Electronics Packaging

#### Walter Trybula

Trybula Foundation, Inc., Austin, TX USA

**Topics:** Emerging Technology, Advanced Lithography, Nanotechnology, Nano manufacturing, Nanomaterials, Environmental issues of Nanotechnology, Business Requirements of Nanotechnology

#### E. Jan Vardaman

TechSearch International, Inc., Austin, TX USA

**Topics:** International developments in semiconductor packaging, manufacturing and assembly; SiP: Business and technology Trends; drivers in advanced packaging; Flip chip and wafer level packaging

#### **Paul Wesling**

Saratoga, CA USA

**Topics:** Using Xplore, and Google Scholar to Mine IEEE's Online Repository of Technical Information; Origins of Silicon Valley and the EPS

#### C.P. Wong

Georgia Institute of Technology, Atlanta, GA, USA

**Topics:** Materials

#### Jie Xue

Cisco Systems, Inc, San Jose, CA, USA

**Topics:** Advanced Packaging for Networking Application; Impact of Internet of Everything (IoE) to Semiconductor Industry eco-system; High performance substrate technologies; Trends and challenges of Silicon Photonics for datacenter and networking applications

#### Kishio Yokouchi

Fujitsu Interconnect Technologies Ltd., Nagano City, Nagano, Japan

**Topics:** Thermal management technologies; Embedded passive component technologies; Chip to chip optical interconnection technologies

#### **CONFERENCE NEWS**

#### The 68th ECTC in San Diego—A Superb Edition Reaching New Heights

his year's IEEE Electronic Components and Technology Conference (ECTC) was held at the Sheraton Hotel in San Diego, California from May 29 to June 1. The conference brought together a total of 1,756 industry professionals, academics, and students in attendance from 28 countries, reaching a new record for ECTC, with more than 200 more attendees compared with previous highest attendance records.

In addition to general attendance, 2018 was the year for setting ECTC records. The Tuesday professional development courses drew a record 480 attendees, and overall sponsors and sponsorship broke the current record set last year in Orlando. The conference included 369 papers in 36 oral sessions and 5 interactive poster sessions. There were five special technical sessions and two special networking receptions with invited panelists. This year's Technology Corner Exhibit featured 106 exhibits—slightly more than last year in Orlando. This is a tribute to the quality of the conference and its attendees.

Preparations for the 68th ECTC started last October, when the professional volunteers serving in the technical committees reviewed 562 submitted abstracts. Ultimately, 66% of the submissions were accepted, leading to 359 presentations at the conference. This year, 48% of the submitted abstracts were from corporations,

and 52% were from academia and research institutions. In a testimony to the diversity of the industry and the conference, abstracts were received from 27 countries.

The conference program came together at the Technical Program Committee's annual planning meeting near Dallas, Texas, on November 2 and 3, 2017. The subcommittee chairs and session chairs did an excellent job developing interesting sessions and communicating with their session authors, which enabled all the manuscripts to be publication-ready well before the start of the conference. ECTC again used, for the third year, the IEEE Computer Society Conference Publishing

The attendance at the 68th ECTC set a new record: 1,756!

68th ECTC offered 18 Professional Development Courses, reaching this year a record attendance of 480 participants.

Speaker Breakfast—Christopher Bower (in the back) providing guidelines to speakers and committee chairs. Session chairs and speakers making last minute preparations for their sessions.

Avi Bar-Cohen/IEEE EPS President (standing) co-chairs together with Chris Bailey, University of Greenwich, the panel session focused on IC Package Co-Design for Heterogeneous Integration.

Boon Chye Ooi (left), Senior Vice President, Global Operations at Broadcom Inc. receives a recognition award as a Keynote Speaker from Sam Karikalan (right) from Broadcom Inc., 68th ECTC General Chair.

Patrick Thompson/Texas Instruments at a great networking reception organized for students.

Services to receive and process manuscripts. As in previous years, the IEEE CrossCheck system was used to ensure that all of the ECTC manuscripts maintain a high level of original content. New for 2018 was implementing the review process performed by the session chairs for all the submitted manuscripts.

As usual, the first day of the conference, the Tuesday following Memorial Day, included professional development courses (PDCs), special sessions, and workshops. Once again, the conference had nine morning PDCs, running from 8 a.m. to noon, and nine afternoon PDCs, running from 1:15 p.m. to 5:15 p.m. The courses continue to

serve as a great source for students and engineers to quickly get "up to speed" on a variety of topics, such as wafer-level and fan-out (FO) packaging, system-in-package (SiP), materials for electronics, and reliability. There were also some newcomers, such as photonic packaging, flexible hybrid electronics, and power electronics.

On Tuesday, ECTC also hosted the Heterogeneous Integration Roadmap Workshop, which took place from 8–5 p.m. The workshop was open to all ECTC attendees. The agenda was divided into four sessions plus a wrap-up session, and covered several topics relevant to heterogeneous integration, from applications such as high-performance computing, consumer, and industrial, to integration processes such as 3D integration and wafer-level packaging, as well as materials and simulation, supply chain, and testing. The wrap-up covered technical working group cross-collaboration, manuscript completions, SEMICON West plans, and 2018 events.

There were two special sessions and one evening plenary panel on Tuesday. All three represented breaks from tradition, as they focused on emerging technologies, and new applications, in a nod to the changing landscape inspired by heterogeneous integration at the system level.

At 10 a.m., Hong Yeo, of Georgia Institute of Technology, and C.S. Premachandran, GLOBALFOUNDRIES, co-chaired an emerging technologies session on "Soft Material-Enabled Electronics for Medicine, Healthcare, and Human-Machine Interfaces." Session speakers included Michael McAlpine, University of

#### **2017 ECTC Best Paper Awards**

#### 1) Best Session Paper

"High Thermal Conductivity Mold Compounds for Advanced Packaging Applications" Makoto Shibuya & Luu Nguyen—Texas Instruments, Inc.

#### 2) Best Interactive Presentation Paper

"Development of Die Attachment Technology for Power IC Module by Introducing Indium into Sintered Nano-silver Joint," ChunAn Yang and C. Robert Kao—National Taiwan University; and Hiroshi Nishikawa—Osaka University

#### 3) Outstanding Session Paper

"Warpage Modeling and Characterization of the Viscoelastic Relaxation for Cured Molding Process in Fan-Out Packages," Shu-Shen Yeh, Po-Yao Lin, Kuang-Chun Lee, Jin-Hua Wang, Wen-Yi Lin, Ming-Chih Yew, Po-Chen Lai, Shyue-Ter Leu, and Shin-Puu Jeng—Taiwan Semiconductor Manufacturing Company, Ltd.

#### 4) Outstanding Interactive Presentation Paper

"Via-in-Trench: A Revolutionary Panel-based Package RDL Configuration capable of 200-450 IO/mm/layer, an Innovation for More-Than-Moore System Integration," Fuhan Liu, Chandrasekharan Nair, Hao Lu, Rui Zhang, Hang Chen, Venky Sundaram, and Rao R. Tummala—Georgia Institute of Technology; Atsushi Kubo and Tomoyuki Ando—Tokyo Ohka Kogyi; Kwon Sang Lee—Disco Corporation

#### 5) Intel Best Student Paper

"Latency, Bandwidth and Power Benefits of the Super CHIPS Integration Scheme," Siva Chandra Jangam, Saptadeep Pal, Adeel Bajwa, Sudhakar Pamarti, Puneet Gupta, and Subramanian Iyer—University of California, Los Angeles

### 6) Texas Instruments Outstanding Student Interactive Presentation Paper Award

"Development of Die Attachment Technology for Power IC Module by Introducing Indium into Sintered Nano-Silver Joint" Chun An Yang and C. Robert Kao—National Taiwan University; Hiroshi Nishikawa—Osaka University

Minnesota; Todd Coleman, University of California, San Diego; Aadeel Akhtar, Psyonic; and Rooz Ghaffari, Epicore Biosystems. The speakers offered expertise on advancements in soft materials, and how they will impact our lives in the future.

The afternoon special session, Frontiers in Assembly, chaired by Florian Herrault, HRL Laboratories, focused on emerging device assembly methods and applications to accommodate the needs of heterogeneous integration at the system level. Speakers Jeff Demmin, DARPA; Stefan Behler, Besi; Matthew Meitl, X-Celeprint; Doris Tang, PlayNitride; and Val Marinov, Uniquarta discussed the latest advancements in assembly technologies for chip packaging, microLED displays, and ultra-thin chip placement for flexible electronic applications.

On Tuesday evening at 7:45 p.m., Avi Bar-Cohen, IEEE EPS President; and Chris Bailey, University of Greenwich co-chaired the panel session titled "IC/Package Co-Design for Heterogeneous

Systems." Panelists represented different segments of the heterogeneous integration supply chain, and included Harrison Chang, Advanced Semiconductor Engineering, Inc.; John Parry, Mentor Graphics; Yong Liu, ON Semiconductor; Xuejun Fan, Lamar University; Madhavan Swaminathan, Georgia Institute of Technology; and Andrew Kahng, University of California, San Diego. Panelists explained the challenges of integrating different components made up of different materials with different properties. The key takeaway from the session was the importance of understanding the interaction between the chip, package, and board.

Let's not forget the networking opportunities that took place prior to Tuesday's plenary session. Again this year, Texas Instruments sponsored the ECTC Student Reception on Tuesday at 5 p.m. A steady stream of student attendees took advantage of the opportunity to mingle and network with industry leaders, in hopes of getting guidance for their job search.

From 6–7 p.m., speakers and session chairs gathered in Grand Ballroom B for the annual General Chair's speaker reception. These receptions provided a great start to the conference, and helped prepare everyone for the following three days filled with technical presentations and networking opportunities.

Each day at ECTC begins with the Speakers Breakfast, in which the presenters and session chairs meet and handle the preparatory work for their respective sessions. The PDC Chair, Kitty Pearsall, provided instructions to the PDC instructors and proctors on Tuesday morning, and Christopher Bower, the Program Chair, hosted these breakfast meetings, and provided instructions and guidance to the speakers and session chairs.

Wednesday marked the start of the technical sessions, with six sessions running in parallel, both in the morning and in the afternoon each day. Wednesday morning started with large crowds in numerous sessions, including "Flexible Electronics, Substrate for High Frequency Applications," "Advances in Wafer and Panel Level Fan-Out Packaging," "3D Design, Assembly and Additive Manufacturing," and "Automotive and Harsh Environment Reliability," "Antenna-in-Package for RF and mm-Wave Systems," and "Warpage and Moisture Characterization." Afternoon topics covered "Low-Temperature Metallic Interconnection Technologies," "Fan-Out Packaging Applications and Architectures," "Flip-Chip Manufacturing Challenges," "Innovative Design, Modeling and Predictions for Reliability," "Emerging Packaging Technologies for 5G and Advanced Computing," and "Sintering Pastes, Transient Liquid Phase and Direct Bonding." The fan-out sessions drew the largest crowds bar far, with attendees lining up outside the door to get a glimpse of the presentations. This demonstrates the importance of this advanced packaging platform. Just like last year, all oral session paper ratings were done only through the ECTC mobile app.

Boon Chye Ooi, Senior Vice President, Global Operations at Broadcom Inc., presented this year's keynote speech at the ECTC luncheon on Wednesday. His presentation, titled "Packaging Advancement to Enable Artificial Intelligence, Autonomous Cars and Wearables in the Near Future: Cost and Implications" focused on what is needed from the packaging community to enable these rapidly growing markets by 2022.

Specifically, Ooi stressed the growing need for 5G technologies to handle all the data traffic that these applications will require. Noting that while 5G will come sooner than we expect, the U.S. will not be the first implement it, due to a lack of infrastructure.

The 68th ECTC had 106 exhibitor booths at the Technology Corner.

Cristina Amon from University of Toronto and iTherm representative (standing) moderating the panel together with Tanja Braun from Fraunhofer Institute for Reliability and Microintegration (IZM), ECTC representative (far right) the Women's Panel. The panelists seated are (from left to right), Kawthan (Kat) Kasim from Boeing Research and Technology, Jayathi Murthy, UCLA Dean of Engineering and Li Ming, R&D Director with ASM Pacific Technology.

68th ECTC had five Interactive Presentation (IP) sessions with a total of 107 presentations, including 20 in the Student IP Session.

Kemal Aygun/Intel (standing) moderating the Plenary Session on Artificial Intelligence.

IC packaging technology will be the key enabler, particularly 2.5D and 3D technologies. Ooi concluded with a call-to-action to enable the supply chain. Assembly yield management needs to be upgraded to fab level to support Big Data. Development of µbump probe and test technologies are needed. Substrates for low-loss mmWave channels on large packages are needed. Low-cost thermal solutions to reduce end-customers' system costs need to be developed. Most importantly, multiple supplier sources for silicon content, packaging raw materials, and substrates and assembly are needed to maintain business continuity.

Awards for best and outstanding papers from last year's (67th) ECTC, both in oral presentation sessions and interactive sessions, were presented by the ECTC 2018 Program Chair, Chris Bower, at this luncheon. Also presented was the Intel Best Student Paper Award for ECTC 2017.

As is customary at the Sheraton venue in San Diego, The Technology Corner exhibit area was located in a marquee tent with a beautiful view of the bay. Attendees didn't seem to mind the opportunity for a short walk outdoors to visit 106 exhibitors. The exhibits enjoyed a steady stream of attendees, with very busy bursts of activity during the breaks from the technical sessions. The exhibitors hosted a reception on Wednesday evening that provided more opportunities for technical and business exchanges with prospective customers and collaborators. The Interactive Presentation sessions were located in the Nautilus Foyer, outside session rooms, and had a high number of patrons studying the presented results.

ECTC and ITHERM teamed up this year to host the Women's Panel and Reception, which focused on the topic, "How to Enhance Women's Participation in Engineering Around the Globe," chaired

The Gala Reception was a great time for socializing by the beautiful shores of San Diego after a day full of technical meetings and brainstorming.

by Cristina Amon, University of Toronto, and Tanja Braun, Fraunhofer Institute for Reliability and Microintegration (IZM). This year's distinguished speakers included Kawthar (Kat) Kasim, Boeing Research and Technology; Jayathi Murthy, UCLA Dean of Engineering; and Li Ming, R&D Director, Enabling Technologies at ASM Pacific Technology, Hong Kong.

Before the panel got underway, Jan Vardaman, Techsearch International, took a few moments to announce that the IEEE Frances B. Hugle Engineering Scholarship, which her company spearheaded in 2013, is fully funded, and will begin awarding annual scholarships this year. She thanked all the companies who have made donations over the years, and showed a short video from the family of Frances. B. Hugle, who also extended their appreciation.

The panelists then discussed their respective career paths, and the challenges women face in the engineering field, as well as the advantages of being a woman in the field. It was interesting to hear

The 2018 ECTC Executive Committee members from left to right: Nancy Stoffel/GE, Assistant Program Chair, Christopher Bower/X-Celeprint Inc., Program Chair, Mark Poliks/Binghamton University, Vice General Chair, and Sam Karikalan/Broadcom Inc., General Chair.

the differing experiences and perspectives, as all the women on the panel were at different stages of their careers, and as a result, had different stories to tell. The discussion ended with a Q & A session with the audience, and was followed by an in-room reception where discussions and networking continued.

While the panel didn't really address how we can attract more women to the field, attendees—both men and women—came away feeling they had learned something.

The Wednesday evening Plenary Session titled "Artificial Intelligence and Its Impact on System Design" was chaired by Kemal Aygun from Intel Corporation, and included presentations from leading foundries and integrated device manufacturers, as well as representatives from academia and software. Speakers included Igor Arsovski, GLOBALFOUNDRIES; Kailash Gopalakrishnan, IBM Corporation; Andrew Putnam, Microsoft Corporation; Madhavan Swaminathan, Georgia Institute of Technology; and Dan Oh, Samsung. The panelists discussed the computing, memory, and power challenges that come from AI, deep learning, and high-performance computing, and the best ways to solve them from a system architecture perspective.

The Thursday morning sessions were well-attended, and covered topics ranging from "Fan-Out and Interposer Interconnections" to "Technology Advances in Nano, Biochemical, Thermal and Flexible Applications" to "Silicon Photonics." Thursday afternoon included sessions on "Interconnect Reliability," "MEMS, Sensor, IoT and Flex," and "Optical Module Integration."

The IEEE EPS Society President, Avi Bar-Cohen, presided over the luncheon on Thursday and presented the EPS Society Awards. The recipients were presented with a plaque and received warm applause from the audience.

The ECTC 2018 Technical Program Committee meeting was held on Thursday at 5:30 p.m. Nancy Stoffel, who will serve as the Program Chair for ECTC 2019, chaired this meeting, and presented the statistics of the 68th ECTC and the timeline for the runup to the 69th ECTC, which will be held in Las Vegas next year. The EPS Representative on the ECTC Executive Committee, C.P. Wong, introduced Rozalia Beica of DowDuPont as the Assistant Program Chair of the 69th ECTC. This meeting also allowed the ECTC technical program subcommittees to connect with potential new members of their committees.

As always, the Gala Reception on Thursday evening was the highlight of the week for the conference attendees, exhibitors, sponsors, and their guests. It was a time to celebrate the success of the ECTC

The 68th ECTC Event Management team.

by socializing and enjoying the excellent food and beverages that were supported by the Gala Reception Gold and Silver sponsors.

Following the Gala Reception, the 2018 IEEE EPS Seminar on "High Density Packaging Technologies in the Era of Big Data" got underway, chaired by Yasumitsu Orii, Nagase, Japan; Shigenori Aoki, Fujitsu. Speakers included Shunichi Kikuchi, Fujitsu; Spike Narayan, IBM Research; Urmi Ray, JCET STATS ChipPAC; Masato Tanaka, Shinko; and Toshihisa Nonaka, Hitachi Chemical. The panelists shared many insights on this evolving segment, bringing different perspectives on the needs and challenges created by Big Data and enabling packaging technologies and materials with a focus on high-density requirements.

Friday sessions continued with more traditional advanced packaging topics, fan-out and TSV-related sessions, as well as a focus on power electronics. The morning sessions ranged from "Fabrication and Characterization of TSV" to "Automotive and Power Electronics" to "Modeling of Power Electronics." The afternoon included sessions on "Advanced Wirebond and Interconnect Technologies," "Next-Generation Materials and Processes for Through Vias and 3D Interconnects," and "Power Delivery Solutions for Components and Systems." At lunch on Friday, everyone had the usual fun at the famous ECTC raffle, where Tom Reynolds, the ECTC Treasurer, kept everyone laughing and longing to hear the numbers on their ticket called.

Overall, the 68th ECTC was the best year yet in terms of its record attendance, strong exhibitor presence, record sponsorship, and number of high-quality technical presentations and submitted abstracts. The ECTC Executive Committee sincerely thanks all the attendees, exhibitors, and conference sponsors for their support as well as all the committee members and chairs who are volunteering their time to help organize the sessions and make ECTC such a success every year. Special thanks also to our event management.

The 69th ECTC will be held at The Cosmopolitan, Las Vegas, Nevada, USA, May 28–31, 2019. Mark Poliks from Binghamton University will be the General Chair of this conference. The Call for Papers and PDC Proposals will be available at www.ectc.net, and the abstract submission will close on October 8, 2018. So get those abstracts ready and submit them as soon as abstract submission opens online.

We are looking forward to see you all in Las Vegas in 2019!

Rozalia Beica Assistant Program Chair, IEEE ECTC 2019

### Article on EPTC on the occasion of its 20th Anniversary

his December 4–7, 2018, we celebrate the 20th Anniversary of the Electronics Packaging Technology Conference (EPTC), our Society's flagship conference in the Asia-Pacific region, which will be held at Resorts World Sentosa, Singapore. To celebrate this historic milestone, the EPS Board of Governors (BoG) will be holding its next meeting in conjunction with EPTC 2018. Although a BoG delegation has attended EPTC in the past, this meeting would be making history as it will be the first-ever BoG meeting outside the USA! It is a concrete demonstration of the internationalisation of our Society and the exponential growth of electronics packaging in Asia. To commemorate this event, we shall give a brief account of the history of EPTC.

The idea for EPTC was mooted by the IEEE Singapore Joint Rel/CPMT/ED Chapter towards the end of 1995. It was felt that there was no Society-sponsored, ECTC-like electronics packaging conference in Asia at that time. It was thought that the great distance between USA and Asia and the expenses involved were preventing many packaging engineers from Asia to attend ECTC. It was then decided to organise an international electronics packaging conference to provide a platform for packaging engineers from all over the world but especially in the Asian region, to exchange ideas and share experiences. The inaugural EPTC was convened on 8-10 October 1997 under the General Chairmanship of Professor Andrew Tay of the National University of Singapore with wide support from universities, research institutes and electronics companies in Singapore. In 2006, in order to steer the long term development of EPTC, the EPTC Board was formed with Prof Andrew as its inaugural Chairman.

EPTC is usually a 3-day conference comprising Professional Development Courses and a Panel on the first day, and keynotes, invited presentations and technical sessions on the remaining two days. The conference is also well supported by a table-top exhibition and sponsorships by companies from all over the world. EPTC has been modelled after ECTC in scope and structure. It has the following 10 categories covering the whole range of topics in electronics packaging:

- 1) Advanced Packaging

- 2) TSV/Wafer Level Packaging

- 3) Interconnection Technologies

- 4) Emerging Technologies

- 5) Materials and Processing

- 6) Equipment and Process Automation

- 7) Electrical Modeling & Characterization

- 8) Mechanical Modeling & Simulations

- 9) Thermal Characterization & Cooling Solutions

- 10) Quality, Reliability and Failure Analysis

Abstracts of papers are reviewed by 10 Technical Committees which are formed from about 120 international experts.

In 2003, our Society's leadership conceived the idea of establishing "flagship" conferences in North America, Asia and Europe. By 2003, after 53 years, ECTC has been well established as the premier electronics packaging conference in the world and our Society's flagship conference in North America. By 2003, a few packaging conferences have sprung up in Asia but EPTC was adopted as our Society's flagship conference in Asia due to several reasons: the topical coverage is good; the conference proceedings are of high

quality; Singapore is able to draw participants from all over Asia (good transportation and facilities); and the standard language there is English (the interchange language chosen by IEEE). In 2006, a new flagship conference was established in Europe, namely the Electronics System-Integration Technology Conferences (ESTC). In fact, the name of the new conference was purposefully chosen so that the triumvirate relationship between the 3 flagship conferences would be evident from their acronyms ECTC, EPTC and ESTC.

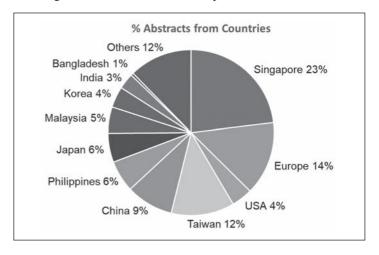

The inaugural conference had only 51 papers and was attended by about 110 conferees but this has grown more than 3 times to 163 papers and 362 conferees in 2017. In 2017, there were 195 abstracts which were received from 24 countries making it a truly international conference indeed. 50% of the abstracts were from industry, 20% from research institutes and 30% from academia making the technical program well-balanced. What is also of great significance is the percentage of abstracts submitted from various main countries as illustrated in the figure below which shows that there is very wide and good contributions from Asian countries as well as good contributions from Europe and USA.

One of the feature highlights of EPTC is the conference banquet cum social event which is usually held in some iconic venues or feature some interesting locations in Singapore. These include the Night Safari (tour through the Singapore Zoo at night), the Malay Heritage Centre, Seafood Centre, new Marina Bay area, Gardens by the Bay, boat tour down historic Singapore River, ride on the Singapore Flyer (giant ferris wheel) and Harbour cruise cum dinner on board ancient Chinese sailing ship. Some of these are shown in the photographs below:

Harbour cruise with buffet dinner on board, EPTC2008.

EPTC2017 Organising Committee in banquet at Marina Bay showing iconic skyline.

This year, the 20th EPTC will be held at the Resorts World Sentosa (RWS) which has many attractions including Universal studios, a casino, an ocean gallery and water theme park as shown below:

Universal Studios.

Casino, Resorts World Sentosa.

Ocean Gallery—Venue of Conference Banquet EPTC 2018.