JANUARY 2021 VOL. 43 NO. 1 ISSN 1077-2999

Driving Innovation in Microsystem Packaging /// EPS.IEEE.ORG

ELECTRONICS

PACKAGING

**SOCIETY** Newsletter

#### **PRESIDENT'S COLUMN**

Chris Bailey University of Greenwich London, UK

As we begin a new year, I would like to thank all our members for your continued support of EPS. With the Covid-19 pandemic affecting many of us, the year 2020 has undoubtedly been a year that many of us would like to forget. Thankfully, with the distribution of vaccines starting worldwide, this pandemic will hopefully be behind us soon. Although this has been a challenging year, I am delighted that our society has progressed steadily towards its strategic goals throughout the last year in our

EEE

areas of membership, chapters, conferences, education, technology, publications, and awards.

Sadly at the end of 2020, we heard the tragic news of the passing of our colleague, mentor, and EPS junior past president—Professor Avi Bar-Cohen. As many of you know, Avi was a leader in thermal sciences and contributed significantly to innovations in thermal management for electronics packaging throughout his career. He will be missed, but his dedication and outstanding contributions to our community continue to inspire us all. A section in the upcoming CPMT transactions will celebrate Avi's lifes work.

Recently, Avi worked with our colleague Vasudeva Atluri to secure donations to endow the society's highest award—the EPS technical field award. I am pleased to confirm that the IEEE Board of Directors has approved the renaming of this endowed award as the Rao Tummala Technical Field Award in honor of Professor Rao Tummala's extensive technical achievements in our field of Electronics Packaging. The awards first recipient will be at ECTC 2022.

In this edition of the newsletter, you can read how we are progressing towards our membership goals. Both Alan Huffman (VP Membership) and Professor Andrew Tay (Student Program Director) detail membership benefits, how to become involved with our chapters worldwide, and some of the latest developments taking place with our growing portfolio of student branch chapters. In terms of education, Professor Jeff Suhling (VP Education) and our functional team for education have been working on our exciting certificate program and a new EPS resource center that will contain webinars and other educational materials for our members. Further details on these will be made available on the website. Our society's goals for technology are also progressing well. Dave McCann (VP Technology) and our functional team for technology have been working closely with our technical committees, who are providing insightful material for our newsletter on specific topics in their specialized areas. In this edition of the newsletter, you can read contributions from our Emerging Technologies, 3D/TSV, and Reliability technical committees. The 2020 edition of the Heterogeneous Integration Roadmap (HIR) will also be made available early in the new year on the society website. My thanks to all our members on the twenty-three HIR technical working groups for making the roadmap an outstanding success.

For EPS, the most important priority is our members, staff, and volunteers' safety and well-being. Hence, many of our meetings and conferences have switched to online platforms while travel restrictions are in place. Recently we held our two regional flag-ship conferences—ESTC (Europe) and EPTC (Asia)—using online platforms with excellent participation from authors, keynote speakers, and delegates. We have come a long way in learning and experiencing what these online platforms can offer, and their capabilities continue to be enhanced. Led by Sam Karaikalan (VP conference), and looking at our conferences post-covid, we are investigating how mixed physical and online conferences could be organized for those conferences interested in running their events in this hybrid format. Guidance for our conference organizers will be made available on the website in 2021.

The end of 2020 also saw newly nominated members join our board of governors (BoG). My sincere thanks to Beth Keser, Grace O'Malley, and Adeel Bajwa, whose terms ended in 2020, for their

(continued on page 17)

#### NEWSLETTER SUBMISSION DEADLINES

15 June 2021 for Summer issue 20211 December 2021 for Winter issue 2022

Submit all material to d.manning@ieee.org

#### **EPS Officers**

President: Chris Bailey, c.bailey@gre.ac.uk

- President Elect: Kitty Pearsall, kitty.pearsall@gmail.com

- VP (Technology): David McCann, david.mccann@averasemi.com

- VP (Conferences): Sam Karikalan, sam.karikalan@broadcom.com

- VP (Publications): Ravi Mahajan, ravi.v.mahajan@intel.com

- VP (Education): Jeff Suhling, jsuhling@auburn.edu

- VP (Finance): Patrick Thompson, patrick.thompson@ti.com

- VP (Membership): Alan Huffman, Alan.Huffman@micross.com

Sr. Past Pres.: Jean Trewhella, jean.trewhella@GLOBALFOUNDRIES.com

**Members At Large**

- 2021 Term End: Regions 1-6, 7, 9—Philip Garrou, Eric Perfecto, Pradeep Lall, Region 10—C. Robert Kao, Chih-Pin (C.P.) Hung, Kishio Yokouchi

- 2022 Term End:Regions 1-6, 7, 9—Rozalia Beica, Xuejun Fan, Subramanian<br/>S. Iyer, Region 8—Tanja Braun, Karlheinz Bock, Region<br/>10—Gu-Sung Kim

- 2023 Term End: Regions 1-6, 7, 9—Mark Poliks, Annette Teng, Patrick McCluskey, Jin Yang, Region 8—Steffen Kroehnert, Region 10—Yoichi Taira, Young Professional—Yan Liu

#### **Publications**

Transactions on Components, Packaging and Manufacturing Technology

Managing Editor: Ravi Mahajan

**Co-Editor Special Topics:** Ravi Mahajan

**Co-Editor, Electrical Performance:** Dale Becker

Co-Editor, Components: Characterization and Modeling: Koneru Ramakrishna

**Co-Editor, Advanced Packaging Technologies:** Kuo-Ning Chiang

**Co-Editor, Electronics Manufacturing:** Muhannad Bakir

#### **Technical Committee Chairs**

Materials & Processes: Bing Dang High Density Substrates & Boards:

Yasumitsu Orii Electrical Design, Modeling & Simulation: Dale Becker

Thermal & Mechanical:

Dereje Agonafer

**Emerging Technology:** Benson Chan

Nanotechnology: Americas: Raj M. Pulugurtha, Chair; Europe: Attila Bonyar, Asia: Jian Cai

**Power & Energy:** Patrick McCluskey

**RF & Thz Technologies:** Manos Tentzeris

Green Electronics: Nils F. Nissen Photonics—Communication, Sensing, Lighting: Gnyaneshwar Ramakrishna 3D/TSV: Peter Ramm Reliability: Richard Rao Test: Pooya Tadayon

#### **Program Directors**

Chapter Programs: Toni Mattila, toni.mattila@investinfinland.fi Awards Programs: Eric Perfecto, Eric.Perfecto.US@ieee.org Student Programs: Andrew Tay, andrew\_tay@ieee.org Industry Programs: William T. Chen, William.Chen@aseus.com Region 8 Programs: Tanja Braun, Tanja.Braun@izm.fraunhofer.de Region 10 Programs: Yasumitsu Orii, yasumitsu.orii@nagase.co.jp

#### **Standing Committee Chairs**

Fellows Evaluation: S.W. Rickly Lee, rickylee@ust.hk Long Range / Strategic Planning: Kitty Pearsall, kitty.pearsall@gmail.com Nominations: Jean Trewhella, Jean.Trewhella@globalfoundries.com

#### **Distinguished Lecturers**

VP Education: Jeff Suhling, jsuhling@auburn.edu

Lecturers: Ramachandra Achar, Mudasir Ahmad, Kemal Aygün, Muhannad Bakir, Ph.D., W. Dale Becker, Wendem Beyene, Karlheinz Bock, Ph.D., Bill Bottoms, Ph.D., Chris Bower, Ph.D., William T. Chen, Ph.D., Xuejun Fan, Ph.D., Philip Garrou, Ph.D., Subu Iyer, PhD., Beth Keser, Ph.D., Pradeep Lall, Ph.D., John H. Lau, Ph.D., Madhu Iyengar, Ravi Mahajan, PhD., James E. Morris, Ph.D., Mervi Paulasto-Kröckel, Ph.D., Eric D. Perfecto, Mark Poliks, Ph.D., Jose Schutt-Aine, Ph.D., Nihal Sinnadurai, Ph.D., Ephraim Suhir, Ph.D., Chuan-Seng Tan, Ph.D., Rao Tummala, Ph.D., E. Jan Vardaman, Paul Wesling, CP Wong, Ph.D., Jie Xue, Ph.D.

#### **Chapters and Student Branch Chapters**

Refer to eps.ieee.org for EP Society Chapters and Student Branch Chapters list

IEEE Electronics Packaging Society Newsletter is published quarterly by the Electronics Packaging Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016-5997. US \$1.00 per member per year is included in Society fee for each member of the Electronics Packaging Society. Printed in U.S.A. Periodicals postage paid at New York, NY, and at additional mailing offices. Postmaster: Send address changes to IEEE EPS Newsletter, IEEE 445 Hoes Lane, Piscataway, NJ 08854. All rights reserved, copyright (c) 2021 by the EP Society of IEEE. Authors and Artists given full permission for further use of their contributions. For circulation information call IEEE Customer Service 800-701-4333, or FAX 908-981-9667.

# Circulate your printed or PDF copy of this NEWSLETTER to co-workers.

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/ whatis/policies/p9-26.html.

#### **EPS NEWS**

#### Chin C. Lee Receives the 2021 IEEE Electronics Packaging Technical Field Award

CHIN C. LEE University of California, Retired Irvine, CA USA

"For contributions to new silver alloys, new bonding methods, flip-chip interconnect, and education for electronics packaging."

The IEEE Electronics Packaging Award, sponsored by the IEEE Electronics Packaging Society, recognizes meritorious contributions to the advancement of components, electronic packaging or manufacturing technologies. The technical field for this award includes all aspects of device and systems packaging, including packaging of microelectronics, optoelectronics, RF/wire-

less and micro-electro-mechanical systems (MEMS), enhancement of technology, impact on the relevant technical community and the profession, benefit to society, and the quality of the nomination.

The 2021 Award will be presented virtually at the 71st Electronic Components and Technology Conference (ECTC), June 2021

Chin C. Lee's innovative bonding methods and materials and new packaging technologies have been integral to developing high-temperature and high-power electronics. His work on silver wire bond reliability resulted in a wider process window, lower cost, and higher yield in packaging components. He also discovered that silver alloy is anti-tarnishing, which has had enormous economic and technical impact for applications including optics, astronomy telescopes, and LED packaging. His fluxless soldering technology has enabled numerous bonding designs and is critical to packaging electronics for applications where oxidation effects from solder materials can be problematic. Lee also developed solid-state flip-chip interconnects and formulated quantum bonding theory. He established a materials and manufacturing technology graduate program in 2007 at the University of California, Irvine, which was one of a few such programs at that time.

An IEEE Life Fellow, Lee is a professor (retired) with the University of California, Irvine, CA, USA.

#### 2020-Mitsumasa Koyanagi and Peter Ramm

*"For pioneering contributions leading to the commercialization of 3D wafer and die level stacking packaging"*

#### 2019—Ephraim Suhir

*"For seminal contributions to mechanical reliability engineering and modeling of electronic and photonic packages and systems."*

#### 2018—William Chen

"For contributions to electronic packaging from research and development through industrialization, and for his leadership in strategic roadmapping."

#### 2017—Paul Ho and King-Ning Tu

"For contributions to the materials science of packaging and its impact on reliability, specifically in the science of electromigration."

#### 2016—Michael Pecht

"For visionary leadership in the development of physics-of-failurebased and prognosticsbased approaches to electronic packaging reliability."

#### 2015-Nasser Bozorg-Grayeli

"For contributions to the advancement of microelectronic packaging technology, manufacturing, and semiconductor ecosystems."

#### 2014—Avram Bar-Cohen

*"For contributions to thermal design, modeling, and analysis, and for original research on heat transfer and liquid-phase cooling."*

#### 2013-John Lau

"For contributions to the literature in advanced solder materials, manufacturing for highly reliable electronic products, and education in advanced packaging."

#### 2012-Mauro J Walker

"For advancing electronic manufacturing, technology and packaging worldwide through technical innovation and coopera-tive leadership in industry, government, academia, and profes-sional organizations."

#### 2011-Rao R. Tummala

"For pioneering and innovative contributions to package integration research, cross-disciplinary education and globalization of electronic packaging."

#### 2010—Herbert Reichl

"For contributions to the integration of reliability in electronics sys-tems, and leadership in research and education in electronics packaging."

#### 2009—George G. Harman

"For achievements in wire bonding technologies."

#### 2008—Karl Puttlitz Sr. and Paul A. Totta

"For pioneering achievements in flip chip interconnection technology and for semiconductor devices and packages."

#### 2007—Dimitry Grabbe

"For contributions to the fields of electrical/electronic connector technology, and development of multi-layer printed wiring boards."

#### 2006-C. P. Wong

"For contributions in advanced polymeric materials science and processes for highly reliable electronic packages."

#### 2005—Yutaka Tsukada

"For pioneering contributions in micro-via technology for printed circuit boards, and for extending the feasibility of the direct flipchip attachment process."

#### 2004—John W. Balde

"For lifetime contributions to tantalum film technology and the introduction of new electronic packaging technology to development and manufacturing."

For additional information on this and other IEEE Technical Field Awards and Medals, to view complete lists of past recipients or to nominate a colleague or associate for IEEE Technical Field Awards and Medals, please visit http://www.ieee.org/awards

#### Renaming the IEEE Electronics Packaging Technical Field Award

The IEEE Electronics Packaging Award was established in 2002, and has been financially sponsored since its inception by the IEEE Electronics Packaging Society (EPS), formerly the IEEE Components, Packaging, and Manufacturing Technology Society (CPMTS). Recipient selection is administered through the Technical Field Awards Council of the IEEE Awards Board. The Award is presented to an individual or a team of not more than three, for outstanding contributions to advancing components, electronic packaging, or manufacturing. The award consists of a bronze medal, certificate, and cash prize of US\$10,000.

In the evaluation process, the following criteria are considered: enhancement of technology, impact on the relevant technical community and the profession, benefit to society, and the quality of the nomination. The technical field for this award includes all aspects of device and systems packaging, including packaging of microelectronics, optoelectronics, RF/wireless, and micro-electromechanical systems (MEMS).

The IEEE EPS approved a proposal to change the name of the IEEE Electronics Packaging Award to the IEEE Rao Tummala Electronics Packaging Award at its Board of Governors meeting in November 2019. Professor Tummala is a visionary technologist, who provided unparalleled leadership in the industry (IBM), academia (Georgia Tech), professional societies (EPS and IMAPS), and around the globe in packaging research, technology development, manufacturing, and products, as well as in education, and in industry-academic collaborations. His efforts served to define the field of modern electronic packaging and his combined impact on the electronic industry, academia, and professional societies around the globe places him at the forefront of the packaging profession.

Beginning with the 2022 nomination process, the award will be renamed the IEEE Rao R. Tummala Electronics Packaging Award and endowed through the IEEE Foundation.

#### Newly-Elected and Appointed Members of the Electronics Packaging Society Board of Governors

n 2019, EPS members elected new Members- at-Large to the EPS Board of Governors for the three-year term of 1 January 2021 through 31 December 2023.

#### **REGIONS 1-6, 7 & 9**

**F. PATRICK MCCLUSKEY** (StM'85-M'91-SM'15) (B.S.('84) Lafayette College; M.S.('86) and Ph.D. ('91), Materials Science and Engineering, Lehigh University) is a Professor of Mechanical Engineering at the University of Maryland, College Park and the Mechanical Engineering Department's Division Leader for Design and System Reliability. He has over 25 years of

research experience in the areas of thermal management, reliability, and packaging of electronic systems for use in extreme temperature environments and power applications. His research has been sponsored by NSF, NASA, DOE, DOD, ARL, ONR, along with leading component, module, and OEM manufacturers in the aerospace, automotive and energy industries.

Dr. McCluskey has authored/co-authored three books and four US patents, as well as over 150 peer-reviewed technical articles with over 3000 citations, including over 40 articles in IEEE journals and major EPS conferences, such as ECTC and iTHERM. He has also served as technical program or general chair of IEEE conferences on high temperature electronics and integrated power electronic packaging (e.g. 3D-PEIM), as well as being the organizer of the President's panel session on Power Module Integration at ECTC 2016. Dr. McCluskey has provided a short course on integrated thermal packaging of power electronics at ECTC and iTHERM since 2013.

He is an associate editor of the IEEE Transactions on Components, Packaging, and Manufacturing Technology, and is currently the chair of the EPS Technical Committee on Energy and Power Electronics, where he has led a team in writing the Integrated Power Packaging chapter of the IEEE Heterogeneous Integration roadmap. He has been a senior member of IEEE EPS since 2015 and an at-large member of the Board of Governors of the Electronic Packaging Society since 2018, where he has been active in the Education Committee, assisting in the development of guidelines for the EPS certificate program. He is a fellow of IMAPS and a member of ASME.

#### STATEMENT OF INTEREST

As heterogeneous integration of diverse components supplants Moore's law as the driver for performance improvement, a unique opportunity is presented to the electronics packaging community to lead next generation electronics products development. Continuing for another term on the Board of Governors will allow me to expand my work with the Education Committee with a focus on working with universities to develop and promote a heterogeneous integration focused electronic packaging curriculum consisting of Webinars and Courses for incorporation into university undergraduate and graduate programs and EPS certificates. Such a curriculum would highlight some of the newer, non-traditional packaging technologies, such as integrated thermal and power packaging and 3D packaging using additive manufacturing. Another goal will be to work with the conferences and publications groups to develop new and expand existing conferences and publication venues to address these critical emerging packaging technologies needed to support heterogeneous integration. I would also use my contacts in the Power Electronics community to further collaborations with the IEEE Power Electronics Society (PELS) to enhance the impact of these efforts. Through these efforts, I hope to assist in making IEEE EPS the leading society for next generation electronics development.

MARK POLIKS (M'04) is Empire Innovation Professor of Engineering, Professor of Systems Science and Industrial Engineering, Professor of Materials Science and Engineering and Director of the Center for Advanced Microelectronics Manufacturing (CAMM) at the State University of New York at Binghamton. In 2006, he established the first research center

(CAMM), to explore the application of roll-to-roll processing methods to flexible electronics and displays, with equipment funding from the United States Display Consortium (USDC) and the Army Research Lab. His research is in the areas of industry relevant topics that include high performance electronics packaging, flexible hybrid electronics, medical and industrial sensors, materials, processing, aerosol jet printing, roll-to-roll manufacturing, in-line quality control and reliability. He has received more than \$20M in research funding from Federal, New York State and corporate sources and more than \$30M in equipment funding from federal and state sources. He is the recipient of the SUNY Chancellor's Award for Excellence in Research. He leads the New York State Node of the DoD NextFlex Manufacturing USA and was named a 2017 NextFlex Fellow. He has authored more than one-hundred technical papers and holds forty-six US patents. Previously he held senior technical management positions at IBM Microelectronics and Endicott Interconnect. Poliks is a member of technical councils for the FlexTech Alliance, NBMC and NextFlex, and on the NextFlex Governing Council. He is an active member of the IEEE Electronics Packaging Society Electronic Component and Technology Conference and served and the 69th ECTC General Chair. Poliks received dual undergraduate degrees, with honors, in chemistry and mathematics from the University of Massachusetts and a Ph.D. from the University of Connecticut in materials science and engineering. He was a McDonnell-Douglas post-doctoral fellow working on solid-state magnetic resonance at Washington University, St. Louis before starting his career at IBM.

#### STATEMENT OF INTEREST

I have been an active member of IEEE and the CPMT Society/ Electronics Packaging Society for sixteen years. During this time, I have served the IEEE EPS ECTC community as a subcommittee member and subcommittee chair (for both materials and processing and interactive presentations), an executive committee member including ECTC General Chair in 2019 and currently serving as junior past general chair. My career has been nearly exclusively dedicated to advancement of materials, processing, fabrication and performance of electronics packaging. I have worked the first half of my career in industry (at the IBM Corporation and Endicott Interconnect) while part-time as a research professor and the second half as a full professor and tenured faculty member at the State University of New York, Binghamton. During this time, the importance of electronics packaging has continued to rise and is currently one of the primary means to achieve continued improvements in systems integration and performance. The IEEE Electronics Packaging Society has a unique opportunity to grow in size, importance and relevance within the larger IEEE community; EPS growth is essential to help to foster dialog and collaboration within the industry on the advancement of packaging and interconnect technologies. I seek to continue my active role in IEEE EPS and to work together with the EPS BOG and its members to help grow the outreach of EPS through new membership, industry roadmap working groups, conferences, peer-reviewed publications and professional education worldwide.

**ANNETTE TENG** (M'97-SM'01) is the Chief Technology Officer at Promex Industries, a manufacturer of electronic and medical components in Silicon Valley, since 2014. She has spent most of her career in electronic component packaging and manufacturing in both corporate and academic environments. Born in Borneo (Malaysia), she left at 16 to attend Sweet Briar College

in Virginia. After Graduating from University of Virginia with a Ph.D. in Materials Science, she moved to Silicon Valley and started her career in the IC world at Signetics. She has worked in components packaging and assembly at Philips Semiconductor, Linear Technology Corp. and Corwil Technology. Prior to joining Promex, she was Package Assembly Manager at Silanna in Australia for 3 years.

She also worked at Hong Kong University of Science and Technology and helped launch their electronics packaging programs from 1997 to 2000. During that time, membership grew and many engineers and researchers working in packaging from Hong Kong chose ECTC to present their papers. Since returning to Silicon Valley in 2000, she had been an officer of the local Santa Clara Valley chapter, which was the main organizer for IEMT. Following trends where manufacturing moved from US to Asia, the IEMT was moved to Malaysia, which has now become the premier packaging conference in Malaysia celebrating its 39th year in 2020. She has published and presented papers at ECTC and MEPTEC in the areas of dicing, thinning, die attach films and package delamination. She has been active in IEEE-EPS Chapter activities in Silicon Valley since 2000 and is currently the Chair of the IEEE-EPS Santa Clara Chapter.

Dr. Teng is the 2018 recipient of IEEE EPS Regional Contributions Award and 1999 IEEE CPMT Presidential Award.

#### STATEMENT OF INTEREST

I have been very active and interested in membership and chapter development for IEEE EPS regional chapter. I am committed to ensure that the EPS chapter is relevant to packaging community through dissemination of knowledge and providing opportunities for all who are interested in electronic packaging.

**JIN YANG** (M'09-SM'17) is a thermal architect with Intel Corporation located in Oregon USA. His research areas include, electronic and photonics packaging, and advanced package, component and system thermal management and microelectronics cooling. He has over 10 years of experiences in the areas of microelectronics manufacturing, electronic packaging and electronics

cooling since he obtained his PhD degree in 2008. He was a senior staff engineer with Assembly, Test Technology Development (ATTD), Intel Corporation focused on next-generation disruptive thermal-mechanical technology development for meeting novel electronic package needs. He holds 14 US patents in the areas of electronic packaging and microelectronic cooling and has published over 30 peer-reviewed journal and conference papers. Prior to join Intel Corporation, Jin Yang obtained a PhD degree from Georgia Tech in Atlanta in the area of electronic packaging. Before that, he obtained his master degree and bachelor degree from Texas A&M University (College Station, TX) and Tsinghua University (Beijing, China) respectively.

Jin is an elected IEEE senior member and serves technical sub-committee chair of IEEE EPS (electronic packaging Society) ECTC and track chair of IEEE ITHERM. He has been a member of IEEE ECTC Assembly and Manufacturing Technology (AMT) committee since 2010 and served as assistant chair and chair for this committee for 2019 and 2020 respectively. During the last four years, he has served as track chair for IEEE IHTERM since 2016.

Outside IEEE, Dr. Yang has a long history of continued service to ASME community in the area of electronic and photonic packaging and has taken a leadership role in ASME Electronic and Photonic Packaging Division (EPPD). He serves as General Chair of InterPACK'2020 conference, flagship conference of ASME Electronic and Photonic Packaging Division (EPPD) and served as program co-chair and track chair in the last four years. He is Associate Editor of ASME Journal of Electronic Packaging (JEP). He once received Journal of Electronic Packaging Associate Editor of the Year Award. He is also a member of K-16 (K-16: Heat Transfer in Electronic Equipment). I served as a liaison for over three years for SRC (Semiconductor Research Corporation) projects between the research institutions and participating companies and helped expedite research work and collaboration between them.

#### STATEMENT OF INTEREST

If I get an opportunity to be selected onto the EPS Board of Governors, I would like to participate and contribute to the activities in the areas of technology and conferences. In the area of electronic packaging, there is a strong connection to the industry and technology convolution and commercialization seems crucial to apply novel ideas and technology to the real applications and solving technical challenges the industry is facing. One program I contributed to has been in full HVM production through 5 years of pathfinding and development with an investment of \$1.5 billion. One program I led goes into HVM production, which saves over tens of millions of dollars per year for the industry through the innovation and continued development. Meanwhile, if given an opportunity to be selected into EPS Board of Governors, I would like to contribute to the activities of conference EPS/IEEE organizes. One area is to establish a more active collaboration in the conference/ event organized by IEEE with ASME technical division, including Electronic and Photonic Division since many professionals make their contributions to the area of electronic packaging through both IEEE EPS and ASME EPPD.

#### **REGION 8**

**STEFFEN KROEHNERT** (M'11) is a well-known component of the Packaging Community for more than 10 years. He is President & Founder of ESPAT-Consulting based in Dresden, Germany. Steffen is providing a wide range of consulting services around Semiconductor Packaging, Assembly, Interconnect Technologies and Test, mainly for customers in Europe. Uti-

lizing his large network in industry, institutes and academic, he also supports small- and medium-sized companies as well as innovative Start-ups to find the right packaging solutions for their products and setup the supply chain from prototypes to small series and High Volume Manufacturing (HVM). Until June 2019, he worked for 22 years in different R&D, engineering and management positions at large IDMs and OSATs in Germany and Portugal, namely Siemens Semiconductors Regensburg (1997-1999), Infineon Technologies Regensburg and Dresden (1999-2006) and Qimonda Dresden and Porto (2006-2009), where Steffen was instrumental in developing FBGA packaging technology for DRAM products. As Director of Technology, he helped setting up and making visible the company NANIUM Porto and Dresden (2009-2017), the largest OSAT in Europe, where Steffen has been heading R&D during introduction of System-in-Package (SiP) and technology transfer and scaling from 200mm to 300mm reconstituted wafer format of the leading Fan-Out Wafer Level Packaging Technology embedded Ball Grid Array (eWLB) from Infineon Technologies. After acquisition of NANIUM by Amkor Technology served as Senior Director Technology Development in Porto and Dresden (2017-2019) working with the European Business Development team. Steffen founded and chaired the European SEMI integrated Packaging, Assembly and Test - Technology Community (ESiPAT-TC) inside SEMI Europe from 2016-2020, serving now as co-chair. His excellence in developing and innovating electronics packaging for semiconductor devices has resulted in authoring and co-authoring of 23 patent filings and many technical papers in the field of Packaging Technology. He co-edited the book "Advances in Embedded and Fan-Out Wafer Level Packaging Technologies". Since 2011, Steffen is co-chair of the Advanced Packaging Conference (APC) committee at SEMICON Europe, which is built of 22 packaging experts from European industry, institutes and academic. Steffen is active member of several technical and conference committees at IEEE EPS, IMAPS, SMTA and SEMI. He holds a M.Sc. degree in Electrical Engineering and Microsystems Technologies from the Technical University of Chemnitz, Germany.

#### STATEMENT OF INTEREST

With more than 20 years in the Semiconductor Packaging, Assembly, Interconnect and Test industry, and active participation in and contribution to industry associations such as SEMI, IEEE EPS, IMAPS and SMTA, I have developed a wide range of knowledge and experience and a very large network, allowing me now to consult mainly small- and medium-sized companies in the field, but also large EDA, Material and Equipment suppliers, in terms of packaging technologies, roadmaps and strategy. I'm focusing on the importance of the collaboration of the complete supply chain and promote a close collaboration. The EPS is a major element supporting the communication between the different players, and fostering collaboration along the semiconductor supply and value chain, and therefore, I want to actively contribute to, but also influence the work of the EPS, representing the European packaging community, supporting events, promoting new memberships, continuous learning, education in the field also to recruit the experts of the future, which have to work more interdisciplinary than ever before. In 2013, I initiated the Industry Interest Group ESPAT with up to 70 member companies, which later in 2015 became the SEMI Special Interest Group (SIG) European SEMI integrated Packaging, Assembly and Test (ESiPAT), today called Technology Community (TC), which I have been chairing for the last 4 years. This TC has the main objective to promote, maintain, strengthen and grow Semiconductor Packaging, Assembly, Interconnect and Test in Europe.

#### **REGION 10**

**YOICHI TAIRA** (M'89-LS'20) received his B.S. degree from Kyoto University and Ph.D. degree from University of Tokyo, both in Physics. From 1983 to1988, he was an Associate Professor with the Institute for Laser Science, University Electro-Communication, Tokyo. From 1988 to 2015, he was a Research Staff with IBM Research mostly in Tokyo. From 1989 to 1990, he was with

IBM T.J. Watson Research Center. In 1998, he became an IBM Senior Technical Staff Member. Since 2015, he has been a Visiting Professor with Keio University. He is also involved in photonic packaging at IBM TJ Watson Research Center. He has been involved in various science and technology areas including technology research on various aspect of lasers including femtosecond laser technology, nonlinear optics, high power laser and UV lasers; VLSI design of memory and CPU; flat panel display technology including liquid crystal and organic light emitting materials; chip packaging including flip chip packaging, underfilling, chip cooling and chip stacking; high performance computer architecture including optical interconnects; nanometer precision fine molding technology, silicon photonic chip packaging and optically transparent adhesives He is the author of 5 books, more than 160 articles, and more than 60 inventions.

Some of the activities he is involved in for governing and administration of academic, society and related organizations include: Chair of IEEE EPS Japan Chapter; Auditor of Japan Institute of Electronics and Packaging (JIEP); General Chair of the 2017 Annual Meetings of Japan Institute of Electronics and Packaging; Chair of Optical Packaging Technology Committee in Japan Institute of Electronics and Packaging; Member of ECTC Materials and Processing Program Subcommittee.

His technical interest includes: Laser science and it application to computer communication; Sensors using optics; Display technology; Precision assembly of electronics/opto-electronic components; Chip cooling and systems cooling; System and network architecture and technology; Technology enabling advanced packaging.

#### STATEMENT OF INTEREST

I will contribute to EPS for its healthy growth through communications and collaborations between members in the region and worldwide and enhance technical activities.

#### YOUNG PROFESSIONAL

YAN LIU (M'14) is a Program Manager at Medtronic Inc. in Tempe, Arizona at United States. She has been working in the Process Development, Manufacturing Integration and Release Product Engineering groups, focusing on both new product introduction and release products of implantable medical devices, as well as developing new electronic packaging solutions and processes

for implantable pacemakers, defibrillators, neurostimulator and other therapies.

Yan received her Ph.D degree in Materials Science & Engineering at Georgia Tech. Her research interest was microelectronics and photonics packaging. She published over 30 peer reviewed journal papers and is a referee for 10 journals including IEEE Transactions on CPMT. She received the Black Belt Certification of Design for Reliability and Manufacturability (DRM). She was the Young Professional Representative in IEEE Electronics Packaging Society in 2018 and a Member at Large since 2019, focusing on engaging young professionals in the EPS community. She initiated and led various Young Professional Events locally and at electronic packaging conferences, e.g. ECTC and ICEPT. She is also a subcommittee member of ECTC Materials and Processing since 2016. She received the IEEE Phoenix Section Outstanding Young Professional Award in 2017, the IEEE CPMT Outstanding Young Engineer Award in 2016, and the Best Paper Award of IEEE Transactions on Components, Packaging and Manufacturing Technology in 2014.

#### STATEMENT OF INTEREST

Engage, develop and increase the young professional (YP) members (target by 100% in 3 years) at different regions of EPS. Continue the YP events at EPS flagship conferences. Form the YP volunteer group to provide networking, career development, mentoring and job opportunities to YPs at different regions.

#### **Congratulations to IEEE EPS Senior Members**

#### **New IEEE EPS Senior Members**

#### The members listed below were elevated to the grade of Senior Member between June and November 2020.

The grade of Senior Member is the highest for which application may be made and shall require experience reflecting professional maturity. For admission or transfer to the grade of Senior Member, a candidate shall be an engineer, scientist, educator, technical executive, or originator in IEEE designated fields for a total of 10 years and have demonstrated 5 years of significant performance. Individuals may apply for Senior Member grade online at: https://www.ieee.org/membership/senior/

Mehmet Arik, Turkey Section Noraini Othman, Malaysia Section Anggoro Widiawan, Indonesia Section Ramesh Kuchibhatla, Seattle Section Michael Cosley, Chicago Section Saranraj Karuppuswami, Southeastern Michigan Section Nandish Mehta, Santa Clara Valley Section Mitul Modi, Phoenix Section Benson Chan, Binghamton Section Stephen Consolazio, Chicago Section Arkaprovo Das, Bangalore Section Yuji Iwai, Santa Clara Valley Section Jakub Korta, Poland Section Dishit Parekh, Schenectady Section Paragkumar Thadesar, San Diego Section

#### Congratulations to the 2021 Newly Elevated IEEE Fellows

isted below are new IEEE Fellows who are members of the EPS. See a list of all EPS members who are IEEE Fellows in the IEEE Fellows Directory.

The grade of Fellow recognizes unusual distinction in the profession and shall be conferred by the Board of Directors upon a person with an extraordinary record of accomplishments in any of the IEEE fields of interest. (Bylaw I-104:11) Nominees shall:

- have accomplishments that have contributed importantly to the advancement or application of engineering, science and technology, bringing the realization of significant value to society;

- hold Senior Member or Life Senior Member grade at the time the nomination is submitted;

- have been a member in good standing in any grade for a period of five years or more preceding 1 January of the year of elevation.

The year of elevation to the grade of Fellow is the year following approval by the Board of Directors conferring the grade of Fellow. Members elevated to the Fellow grade may use the title immediately following approval by the Board of Directors.

The IEEE Fellows, an elite global group with international recognition are called upon for guidance and leadership as the world of electrical and electronic technology, continues to evolve.

#### **Deepak Goyal**

for contributions to fault isolation and failure analysis

#### **Daoqiang Lu**

for development of materials and manufacturing processes for mobile devices

#### **Gamal Refai-Ahmed**

for leadership in thermal management of electronics product development

#### **EPS Membership Benefits**

As the new year begins, all of us with the Electronics Packaging Society want to wish you the best for 2021. The new year also means we are closing in on the end of the membership renewal period in February, so now is a good time to provide our members some reminders of the benefits that come with their IEEE and EPS membership and provide updates on some of the membership-related activities that EPS is working on.

Saying that 2020 was a challenging year is an understatement, and IEEE and EPS provide a number of resources that are available to our members that can be helpful in both their professional and personal lives. Your EPS membership allows you to access an extensive library of online webinars on a variety of electronic packaging topics that are free for EPS members to access and view at any time. These webinars will soon be available through a new IEEE digital library interface that will be activated in early 2021. The EPS Certificate Program recognizes members for participating in webinars and other EPS technical activities through the accumulation of Professional Development Hours. The EPS Certificate Program is not only a way for members to acknowledge their technical efforts; it can also be an excellent professional development opportunity for managers and leaders to consider for their employees. EPS members receive online access to our society's journal, the IEEE Transactions on Components, Packaging and Manufacturing Technology, as part of their membership and receive discounts to a number of other IEEE journals as well. IEEE provides a number of helpful membership benefits in the form of discounts on various products and services, including technical publications and books, insurance, and IEEE society events and conferences. A complete list of these benefits can be found on the IEEE website at https://www.ieee.org/membership/benefits/index.html.

Hopefully, you saw the EPS survey that was emailed to all our members in December and took a few minutes to fill out. This survey will help us understand our member's opinions on the various member benefits and programs offered by EPS and will serve to inform members about benefits they may not have known about. The results of this survey are expected in early January and we will be providing a summary of the findings and actions soon after.

One of our primary membership focus areas for 2021 will be in identifying and supporting members who are eligible for elevation to Senior Member. Members who have been in an IEEE-designated field for a total of 10 years and have demonstrated 5 years of significant performance are eligible to apply for elevation to Senior Member online. If you know someone who would be a candidate for elevation to Senior Membership, we hope you will suggest and support his or her application!

Finally, we want to mention our chapters and student chapters around the world. Getting involved in a chapter is a great way to net-

#### **Student Chapter Promotion Programs**

by Dr Andrew Tay, EPS Director of Student Programs

To promote the formation and continuation of EPS student chapters, EPS has recently initiated a couple of promotion programs. The Student Chapter Promotion Program (SCPP) is aimed at the formation of new student chapters while the Student Chapter Continuation Program (SCCP) is aimed at helping existing student chapters to remain viable.

#### Student Chapter Promotion Program (SCPP)

Under the SCPP, six students from any university which has an IEEE student branch who are willing to serve as executive committee (exco) members in a new student chapter will be given free IEEE+EPS student memberships. The exco must ensure that their student chapter remains viable for the year. This includes the organization of at least two technical activities per calendar year, holding of annual elections and timely submission of required activity and financial reports every year.

Additionally, faculty members who are willing to serve as Advisors to new student chapters will also be given free IEEE+EPS eMemberships where available, otherwise regular memberships will be provided. The Advisor's duties include advising on student chapter activities, endorsing financial statements where necessary, ensuring that annual election of new student exco members are held before end December, and required reports are submitted by the student exco in a timely manner every year.

An evaluation on the performance of subsidized student exco members and Advisors will be conducted in January each year based on reports submitted. Non-performing students and Advisors will not be subsidized for another year. While Advisors may be subsidized every year, student exco members can only be subsidized a maximum of two times in order to encourage a healthy succession of student leaders in the chapter.

The first phase of the SCPP for 5 new student chapters was launched in May 2019 and was over-subscribed by one. All 6 applicants were eventually approved. They are: Michigan State University, University of Florida, University of Maryland, Fudan University, State University of New York at Binghamton and Florida International University

A second phase of the SCPP to facilitate the formation of 10 more new student chapters in 2020/21 was launched in December 2019. work with other professionals in your area. The growth in our student chapters over the last 2 years has been tremendous with students and advisors organizing new chapters. EPS has established a program to provide financial assistance to existing and new student chapters. IEEE student members are also eligible for a special one-time 50% discount elevation from Student to Member grade upon their graduation through the IEEE Student Transition Elevation Partnership (STEP) program.

If you have questions or concerns about your EPS membership and the benefits that are included, please reach out to us...we want to help you get the most out of being part of EPS!

> Alan Huffman VP Membership

Any student or faculty who are interested to form new EPS student chapters in their universities, *whether they are currently IEEE members or not*, can submit applications to the EPS Director of Student Programs, Dr Andrew Tay by emailing him at andrew\_tay@ieee.org listing the names and email addresses of 6 students from the same university who are committed to serve as exco members in the new student chapter, and the name and email address of a faculty who is committed to serve as the chapter Advisor. To date, under this second phase, 3 EPS student chapters have been established in the TU Cluj-Napoca, Romania; Georgia Institute of Technology, USA; University of Waterloo, Canada. One more university, Wuhan University, China, has been supported and is presently awaiting IEEE approval of their petition to form a new EPS student chapter.

#### **Student Chapter Continuation Program (SCCP)**

Another program, the Student Chapter Continuation Program (SCCP) has also been initiated to facilitate the continuation of existing EPS student chapters. Similar free IEEE+EPS memberships will be given to six students in a university with an existing EPS student chapter who are willing to serve as executive committee (exco) members in the student chapter, and to a faculty who agrees to serve as the Advisor to the student chapter. For this initial launch, any student or faculty who are interested to continue the existing EPS student chapter in their universities, whether they are currently IEEE members or not, can submit applications to the EPS Director of Student Programs, Dr Andrew Tay by emailing him at andrew\_tay@ieee.org listing the names and email addresses of 6 students from the same university who are committed to serve as exco members in the student chapter, and the name and email address of a faculty who is committed to serve as the chapter Advisor. The existing EPS student chapters are at Tsinghua University, Politechnica Univ of Bucharest, Universidade Federal do ABC, Singapore University of Technology & Design, Universidade Estadual Paulista-Guaratingueta, San Jose State University and University of California-Los Angeles.

#### **Annual Subsidy for Student Chapters**

To support the organisation of technical activities by student chapters, the exco may apply for subsidies of US\$1000 per annum from EPS. For new chapters in their first year, the subsidy is US\$1500.

Technical Webinars by Electronics Packaging Society (EPS) Organized by Universiti Malaysia Perlis (UniMAP) in Conjunction with IEEE Day 2020 (Compiled by Ir. Dr. Banu POOBALAN)

EEE Day is an annual celebration event hosted by Universiti Malaysia Perlis (UniMAP) and several IEEE societies including Electronics Packaging Society (EPS). IEEE Day for the first time in the history was celebrated when engineers worldwide and IEEE members gathered to share their technical ideas in 1884. IEEE Day celebration carries the theme, which emphasizes on Leveraging Technology for a Better Tomorrow. While the world benefits from what's new, IEEE focuses on what's next. IEEE Day is celebrated on the first Tuesday of every October as an annual event. In the year of 2020, for the 11th consecutive year, IEEE Day worldwide celebration was initiated on Tuesday (6th October 2020) and continued throughout the first two weeks in October.

In conjunction with IEEE Day 2020, EPS once again succeeded in its mission of constantly motivating the local engineering community with technical knowledge sharing session from the internationally respected speakers. However, due to the Covid-19 pandemic, this year, the technical sharing was conducted via online webinars.

It's our honor to have invited semiconductor packaging industry's notable speakers, presenting three topics of interest: (1) First Speaker: Dr Andy Mackie (Principal Engineer & Manager, Thermal Interface Material Applications, Indium Corporation) on "What's Driving—Automotive Electronics Assembly and Packaging" (2) Second Speaker: Prof Chris Bailey (President, IEEE Electronics Packaging Society) on "Overview of the IEEE Electronics Packaging Society" (3) Third Speaker: Dr Ravi Mahajan (Director, Technology & Manufacturing Group Intel Corporation) on "Direction and Opportunities in Heterogeneous Integration using Advanced Packaging".

Dr Andy Mackie covered the introductory overview of advanced automotive packaging technology trends, main market players and a prospective outlook on related future growth. This talk was attended by over 200 participants; mainly from industry, academic and international backgrounds. Prof Chris Bailey highlighted on the overview of IEEE EPS, achievements, membership benefits and packaging technology advancement. This talk was attended mainly by academics, industry key players and Heterogeneous Integration with some international participants. The third speaker Dr Ravi Mahajan discussed about the technology opportunities and challenges in

Figure 2. The webinar delivered by Prof Chris Bailey from president of IEEE Electronics Packaging Society.

heterogeneous integration of Interconnect in 2D and 3D. This talk was well received by industry, academicians and international participants.

We would also like to thank Universiti Malaysia Perlis (Uni-MAP) for the continued commitment and support of this annual event. We are looking forward for a grand IEEE Day 2021 event next year once COVID-19 is behind us!!!

#### Technical Webinars by Electronics Packaging Society (EPS)

(Compiled by Ir. Dr. Banu POOBALAN)

PS Webinar Series 2020/21 event hosted by Electronics Packaging Society (EPS) Malaysia Section consist of a string of webinars conducted online as a knowledge sharing platform for participants from all over the world in the industry

Figure 1. The webinars schedules, topic titles and speakers information

and academic fields. The Webinar Series 2020/21 initiated in the month of December 2020 and it will be continued throughout the year of 2021.

It's our honour to have invited one of the semiconductor packaging industry's notable speakers, Dr HongWen Zhang presenting topic entitled "The Evolution of Lead-free Solder Alloys". Dr. HongWen Zhang is Manager of the Alloy Group in Indium Corporation's Research & Development Department. His focus is on the development of lead-free solder materials and the associated technologies for high-temperature and high-reliability applications. Dr. Zhang has extensive experiences in various aluminum (Al) alloys and fiber/particle-reinforced Al-based composite materials, and Al-rich and ZrHf-based amorphous alloys. The webinars schedule, topic title and speakers information as per presented in Figure 3.

This talk highlighted the evolution of lead-free solder alloys. As the world is moving towards green manufacturing, lead-free soldering, originally driven by RoHS (Restriction on the use of Hazardous Substances in electrical and electronic equipment) of Europe, the Sn-rich alloys, including SnAgCu, SnAg and SnCu were becoming the mainstream for electronic industry. While the electronic industry keeps advancing rapidly towards miniaturization, two more important drivers actually dictate the evolution of lead-free solders-low cost, and high reliability. This talk briefed the evolution of lead-free solders after the implementation of leadfree soldering in industry from 2006, covering (1) the first generation high-Ag SAC solders; (2) the low Ag/zero Ag Sn-rich solders; (3) the high-reliable SAC solders; (4) the low temperature leadfree solders and (5) high temperature lead-free bonding materials. In each session, the market need, the pros and cons of the representative materials in each group were discussed. This webinar was attended mainly by academics and industry key players with some international participants.

Figure 3. Webinar schedules, topics and speakers information.

In summary, this technical webinars were very informative, of all participants truly get inspired by the quality and quantity of late-breaking developments of emerging lead-free solder alloys technologies. We on behalf of EPS Malaysia Section would also like to thank Dr HongWen Zhang for his commitment and valuable sharing via this series webinars.

#### 39th International Electronics Manufacturing Technology (IEMT) & 23rd International Electronics Materials and Packaging (EMAP) Conference 2021

- Plenary Speech

- o Packaging Technology and Al

- o 5G Technologies and Applications

- o IoT and Big Data

- Special Session

- o Heterogeneous Integration Forum / Wafer Level Packaging / 3D SiP Integration

- Student career prospective talks by industry leaders Share your Life story / The role models (Fully Sponsor for University Students)

- Industry Session

- o Power Modules for HEV/EV, Automotive packaging Forum

#### SCOPE OF PAPERS SOLICITED

- Advanced Packaging 2.5D, 3.0D, TSV, interposer, flip-chip, SiP, PoP, FOWLP, FOPLP,

- embedded & advanced substrates, heterogeneous integration.

- Assembly and Manufacturing Technology

- Thermal/Mechanical/Electrical Simulation & Characterization

- Material & Processing

- Emerging Packaging & Interconnections Technologies Opto-electronics, Medical Electronics, Nano Technology, Wearable Electronics.

- LED, MEM & Sensor Packaging & IoT

- IC Testing Technology

- Surface Mount Technology

- Quality, Reliability & Failure Analysis

- □ High-Speed, Wireless & Components

This year, we are introducing mentoring session to improve the full paper quality. Drop us email for those who are interested to be the mentor or mentee.

#### **PUBLICATIONS NEWS**

#### Call for Papers Special issue in the memory of Professor Avram Bar-Cohen

Professor Avram Bar-Cohen, past President of IEEE Electronics Packaging Society, and past Editor-in-Chief of the IEEE Transactions on Components and Packaging Technologies passed away on October 10, 2020. He was a giant in the field of thermal management, and made seminal research and professional contributions over a five decade period. Professor Bar-Cohen's research focused on several areas in microsystems packaging. His work on air cooling focused on optimization of natural and forced air cooling devices, and sustainability and life cycle considerations of thermal management devices. His work spanned the spectrum from fundamental research to emerging applications, including 2.5D and 3D heterogeneous integration, radio frequency, optoelectronics, and power electronics devices and systems.

Professor Bar Cohen's research on two-phase heat transfer focused on submerged condensers, pool boiling of dielectric coolants, enhanced surfaces, flow boiling in microgaps, and flow regime characterization in microchannels. With the ongoing move towards heterogeneous integration and three-dimensional packaging technologies, Professor Bar-Cohen recognized the potential of evaporative cooling for such applications. While serving as Program Manager for the Defense Advanced Projects Research Agency (DARPA), he initiated the IceCool Fundamentals program for the exploration of high exit vapor quality two-phase cooling for emerging microelectronics architectures. During 2020, he co-organized a workshop under the sponsorship of the Office of Naval Research to assess understanding of evaporative thermal management and identify research gaps and barriers to implementation of this cooling technique, with a particular focus on fundamental understanding of high vapor quality two-phase flows.

A Special Issue of the IEEE Transactions on Components, Packaging and Manufacturing Technology is planned for publication in 2021. Papers on analytical, numerical, and experimental investigations of thermal management of microsystems are solicited for this Special Issue. Topics include, but are not limited to, the following.

Computational simulations of single and two-phase cooling Air cooling enhancements Optimization of air cooled systems Sustainability considerations in design of thermal packaging Thermal management of 2.5D and 3D heterogeneous microsystems Thermal management of emerging radio frequency, optoelectronics, and power electronics devices and systems Fundamentals of boiling processes in micro/nanoscale devices and systems Two-phase thermal management devices Novel metrology techniques for two-phase flow Materials and surface enhancements in boiling Capillary flow driven two-phase devices Multi-disciplinary cross-cutting topics in liquid cooling, including fluids, reliability, erosion modeling The Special Issue is planned to be published in July 2021, in memory of Professor Bar-Cohen's 75<sup>th</sup> birthday. The publication deadlines are:

Draft manuscript submission: January 30, 2021 Author notification on manuscripts: March 15, 2021 Revised manuscripts due: April 15, 2021 Final decision on manuscripts: April 30, 2021 Final manuscripts due: May 15, 2021

The following organizers of the Special Issue may be contacted for further information or questions.

Dr. Sushil H. Bhavnani Henry M. Burt, Jr. Professor Department of Mechanical Engineering Auburn University <u>bhavnsh@auburn.edu</u>

Dr. Madhusudan Iyengar Principal Engineer Google Inc. miyengar@google.com

Dr. Yogendra Joshi Professor and McKenney/Shiver Distinguished Chair George W. Woodruff School of Mechanical Engineering Georgia Institute of Technology Yogendra.Joshi@me.gatech.edu

Dr. Michael Ohadi Minta Martin Professor of Engineering Department of Mechanical Engineering University of Maryland, College Park <u>Ohadi@umd.edu</u>

Dr. Mark Spector Program Officer Office of Naval Research Advanced Naval Platforms Division, Code 331 <u>Mark.Spector@navy.mil</u>

#### Electronics Packaging Society Section Within IEEE Access

The Electronics Packaging Section within IEEE Access will draw on the expert technical community to continue IEEE's commitment to publishing the most highly-cited content. The Journal peer-review process targets a publication period of 6 weeks for most accepted papers. This journal is fully open and compliant with funder mandates, including Plan S.

This is an exciting opportunity for your research to benefit from the high visibility of IEEE *Access*. Your work will also be exposed to 5 million unique monthly users of the IEEE *Xplore*® Digital Library.

#### Scope

The IEEE Electronics Packaging Society section in IEEE Access covers the scientific, engineering, and production aspects of materials, components, modules, hybrids and micro-electronic systems for all electronic applications, which includes technology, selection, modeling/simulation, characterization, assembly, interconnection, packaging, handling, thermal management, reliability, testing/control of the above as applied in design and manufacturing. Examples include optoelectronics and bioelectronic systems packaging, and adaptation for operation in severe/harsh environments. Emphasis is on research, analysis, development, application and manufacturing technology that advance state-of-the-art within this scope.

#### Get Published in the New Electronics Packaging Society Section of IEEE Access

Go to: https://mc.manuscriptcentral.com/ieee-access

Select the Electronics Packaging Society (EPS) Section from the pull-down menu of "Manuscript type" in the first page of the submission process.

#### **Author Information and Instructions**

EPS is committed to supporting authors and researchers with IEEE Author Tools including the IEEE Publication Recommender, IEEE Graphics Analyzer, LaTeX Analyzer and more. Discover the tools available at the IEEE Author Center - https://ieeeauthorcenter.ieee. org/ieee-author-tools/.

The EPS is regarded as a trusted and unbiased source of technical information for dialog and collaboration to advance technology within the computing community. EPS is led by researchers and technology professionals who are at the center of respected electronics packaging communities where readers and authors already come together.

The articles in this journal are peer reviewed in accordance with the requirements set forth in the IEEE Publication Services and Products Board Operations. Each published article is reviewed by a minimum of two independent reviewers using a single-blind peer review process, where the identities of the reviewers are not known to the authors, but the reviewers know the identities of the authors. Articles will be screened for plagiarism before acceptance.

#### Article Processing Charge (APC): US\$1,750

IEEE Members receive a 5% discount. IEEE Society Members receive a 15% discount. These discounts cannot be combined.

#### **Topical Editors**

Ravi Mahajan, Intel Corporation, USA Dale Becker, IBM Inc., USA Muhannad Bakir, Georgia Institute of Technology, USA Koneru Ramakrishna, Cirrus Logic, Inc., USA Kuo-Ning Chiang, National Tsing Hua University, Taiwan

#### Most Popular Articles According to Xplore® Usage Statistics

#### **3-D Printed Metal-Pipe Rectangular Waveguides**

Mario D'Auria; William J. Otter; Jonathan Hazell; Brendan T. W. Gillatt; Callum Long-Collins; Nick M. Ridler; Stepan Lucyszyn Publication Year: 2015, Page(s):1339–1349

#### Air Jet Impingement Cooling of Electronic Devices Using Additively Manufactured Nozzles

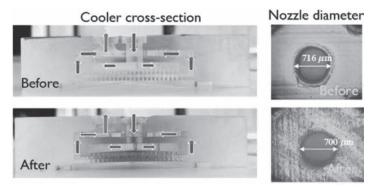

Beomjin Kwon; Thomas Foulkes; Tianyu Yang; Nenad Miljkovic; William P. King Publication Year: 2020,Page(s):220–229

#### Demystifying Machine Learning for Signal and Power Integrity Problems in Packaging

Madhavan Swaminathan; Hakki Mert Torun; Huan Yu; Jose Ale Hejase; Wiren Dale Becker Publication Year: 2020,Page(s):1276–1295

#### Adaptive 5G Architecture for a mmWave Antenna Front-End Package Consisting of Tunable Matching Network and Surface-mount Technology

Jaehyun Choi; Dooseok Choi; Jongwoo Lee; Woonbong Hwang; Wonbin Hong

Publication Year: 2020, Page(s):1-1

#### 77/79-GHz Forward-Wave Directional Coupler Component Based on Microstrip and SIW for FMCW Radar Application Yongrong Shi; Xin Yi; Wenjie Feng; Yongle Wu; Zhengyong Yu; Xingcheng Qian Publication Year: 2020,Page(s):1879–1888

#### **EDUCATION/CAREER NEWS**

#### **Comprehensive EPS Certificate Program**

The IEEE Electronics Packaging Society is pleased to announce that it has expanded its Certificate Program to include a new *EPS Distinguished Achievement Certificate*. This new level of recognition builds on the initial *EPS Achievement Certificate* aimed at early-career professionals, and provides a pathway for mid-career to late-career professionals to highlight their more advanced level accomplishments.

#### **EPS** Achievement Certificate

The EPS Certificate Program was initially established in January 2019 to encourage continuing education and professional development of EPS members. The original offering consisted of an EPS Level One Achievement Certificate that can be earned by completing 15 Professional Development Hours (PDHs) of continuing education in the area of electronics packaging. A variety of mechanisms exist to satisfy the continuing education requirement including attending online IEEE EPS Webinars (1 PDH per 1 hour webinar), attending registered Professional Development Courses (PDCs) at one of the EPS Conferences (ECTC, EPTC, and ESTC) (1 PDH per hour of PDC course attendance), authoring papers at EPS sponsored conferences and the IEEE CPMT Transactions that are published in IEEE Xplore (5 PDH per published conference/journal paper), and serving as a reviewer for IEEE CPMT Transactions papers (5 PDH per 3 reviews completed). Once an EPS member has achieved at least 15 PDHs through a combination of the above approaches, he/ she can then self-nominate for the Certificate via an online form at https://eps.ieee.org/education/eps-certificate-program.html.

The first level *EPS Achievement Certificate* is aimed at earlycareer professionals working in the field of electronics packaging. It is especially intended to encourage the career development of young professionals including advanced graduate students. To date, over 25 EPS members have been recognized. Since there was an overwhelming response to the initial program, the EPS

Vice President Education formed an adhoc Committee from members of the EPS Education Functional Team to further develop the Certificate Program. In particular, the goal was to add a new more advanced certificate that could capture an individual's technical growth, technical and service contributions, and other achievements. This process resulted in the establishment of a new *EPS Distinguished Achievement Certificate* that was recently approved by the EPS Board of Governors.

#### **EPS Distinguished Achievement Certificate**

This new level of recognition builds on the *EPS Achievement Certificate* that is earned by achieving 15 PDHs of continuing education, and provides a pathway for mid-career to late-career professionals to highlight their more advanced level continuing education and career accomplishments. The new *EPS Distinguished Achievement Certificate* will be awarded for advanced technical and service

contributions to the industry and EPS. Two different categories of recognition are offered:

- Distinguished Achievement Certificate for Technical Leadership and Expertise

- Distinguished Achievement Certificate for Professional Engagement and Service

For either area of recognition, the nominee's strengths will be evaluated against prescribed criteria described in more detail below. As with the *EPS Achievement Certificate*, people interested in receiving the *EPS Distinguished Achievement Certificate* must self-nominate via an online Form. The nominee should first review the specific certificate requirements in each recognition area, and choose which one he/she wants to apply. The nominee should review the certificate requirements to assess themselves against the criteria and to prepare their supporting paperwork.

#### Distinguished Achievement Certificate for Technical Leadership and Expertise

There are five high-level focus areas for this new certificate. These areas include: (1) being recognized authority of technical expertise in one's field; (2) being a subject matter expert (SME) at conferences, keynotes, webinars, blogs; (3) demonstrating sustained technical contributions to industry; (4) documenting advanced technical recognitions; and, (5) being endorsed strongly by others. Examples of being a recognized authority of technical expertise include being an advanced member of the technical staff at a company (e.g. Fellow, Senior Technical Staff, Distinguished Engineer, etc.), making technical contributions as a Member or Fellow of professional associations/societies related to electronics packaging (e.g., IEEE, IMAPs, SMTA, ASME, etc.), and being an invited speaker at companies, technical conferences, and EPS Chapter meetings. Methods to demonstrate participation as a SME include abstracts accepted and papers presented at conferences, giving keynote lectures at conferences or professional society meetings, presenting webinars for EPS and other IEEE Societies, and serving on technical panels at conferences and other venues. Example approaches to demonstrate sustained technical contributions to

industry include publishing well-cited technical papers at conferences and in journals, book chapters, and patents; serving as an editor of a journal or reference book; and being a leader or participant in industry blogs, focus groups, technical roadmaps, newsletters, and forums. Methods to document technical recognitions include receiving technical awards from a company, institute, professional society, or academic institution; being the acknowledged inventor of a seminal technology or process important to industry; serving as the point person for global high-level task force activity; and being elected to be a Member of an organization such as the US National Academy of Engineering, Royal Academy of Engineering, Chinese Academy of Engineering, IBM Academy of Technology, etc.

#### Distinguished Achievement Certificate for Professional Engagement and Service

There are four high-level areas of focus for this new certificate. These areas include: (1) demonstrating leadership in the electronics packaging field; (2) illustrating broad impact/influence in the electronics packaging field, (3) providing extensive service and "give back" to the profession and/or industry; and (4) being endorsed strongly by others. Leadership and broad impact activities in electronics packaging can be documented from outstanding accomplishments during industry employment or for notable volunteer contributions to the profession and society. Examples of significant professional service include serving as an officer in a technical society at the international, national, or local chapter level; participating in packaging related technical committees, councils, or affinity groups; contributing to technology roadmaps such as the Heterogeneous Integration Roadmap (HIR); and receiving a professional society or industry award based on service contributions. Documentation of "give-back" to one's technical community can be accomplished via demonstrations of coaching and mentoring of co-workers, young professionals, and students.

More details on the Certificate Program are available on the EPS website at https://eps.ieee.org/education/eps-certificate-program.html. The EPS Certificate Program is sponsored by the IEEE EPS VP Education and is offered only to EPS members. For questions, please contact Jeff Suhling (jsuhling@auburn.edu).

#### **EPS Resource Center**

The IEEE EPS Resource Centers contains valuable, technical content from reputable experts to enhance research or industry work, implement trainings, or earn CEU/PDH credits--all of which are universally available on demand.

- IEEE EPS Resource Centers benefits include:

- · Access to valuable technical community content

- Access to content 24 hours a day, 7 days a week through an easy-to-use global portal

- Available at no cost for EPS members

- Opportunities to earn CEUs and PDHs

Top webinars:

- Interconnects for 2D and 3D Architectures

- Heterogeneous Integration Roadmap Driving Force and Enabling Technology for System of the Future

- Overview of the High-Performance Computing Chapter of the Heterogeneous Integration Roadmap

- Thermal Management Challenges and Opportunities for Heterogeneous Packages

- Power Electronics Packaging, Reliability, and Thermal Management

https://resourcecenter.eps.ieee.org/

Upcoming webinars from the EPS Santa Clara Valley (SCV) Chapter. If your Chapter is interested in co-sponsoring, please contact the SCV Chapter Chair—annette@ieee.org.

You can register here: https://ieee-region6.org/scv-eps/

| Virtual<br>for 2021   | California<br>Time      | Speaker<br>Location      | Title                                                                                                 | Speaker                                     |                                | Speaker Affiliation |

|-----------------------|-------------------------|--------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------|---------------------|

| Jan 28,<br>2021       | Noon                    | St. Paul, MN             | High performance & reli-<br>able aerosol jet printed 3D<br>interconnects for bare die &<br>components | Bryan Germann                               | bgermann@optomec<br>.com       | Optomec             |

| Feb 11,<br>2021       | Noon                    | San Jose                 | Design analysis of chiplet<br>interfaces for heterogenous<br>systems                                  | Wendem<br>Beyene, DL                        | wendem@gmail.com               |                     |

| Feb<br>24–26,<br>2021 | Half days<br>for 3 days | Binghamton               | HIR 4th Annual Meeting                                                                                | 12 Working<br>Group sessions<br>over 3 days | william.chen@aseus<br>.com     |                     |

| Mar 18,<br>2021       | Noon                    | Auburn, AL               | Additively-printed mul-<br>tilayer flexible substrates<br>with Z-axis interconnects                   | Pradeep Lall,<br>DL                         | lallpra@auburn.edu             | Auburn U.           |

| April 15,<br>2021     | Noon                    | Helsinki,<br>Finland     | Sustainable electronics                                                                               | Mervi Paulasto-<br>Krockel, DL              | mervi.paulasto@<br>aalto.fi    | Aalto U., Finland   |

| May 13,<br>2021       | Noon                    | Boston, MA               | Packaging for quantum computing                                                                       | Rabindra Das                                | rabindra.das@ll.mit<br>.edu    | MIT Lincoln Lab     |

| June 10,<br>2021      | 8:00 AM                 | St. Florian,<br>Austria  | Low temperature wafer bonding                                                                         | Jurgen<br>Burggraf                          | j.burggraf@evgroup<br>.com     | EVG                 |

| June 17,<br>2021      | 8:00 AM                 | Enschede,<br>Netherlands | Photonics assembly                                                                                    | Brad Snyder,<br>Jeroen Duis                 | bradley.w.snyder@<br>gmail.com | PHIX                |

#### **President's Column** (Continued from page 1)

contributions to our community during their time on the BoG. And a warm welcome to our new and continuing members—Mark Poliks, Patrick McCluskey, Annette Teng, Jin Yan, Xuejun Fan, Steffan Kroehnert, Yoichi Taira, and Yan Liu. I am also delighted to welcome Kitty Pearsall as our new President-Elect.

The coming years are exciting times for our society, with developments in electronics packaging viewed as a critical differentiator for future electronics systems by the whole electronics industry. I look forward to working with the EPS Board of Governors and our volunteers worldwide throughout 2021 to deliver our strategic goals and continue to provide the unique service that IEEE EPS can offer you, our members, and our industry.

Please stay safe, stay well, and hopefully, there will be opportunities to meet in a less-distanced manner soon.

Chris Bailey

#### **CONFERENCE NEWS**

#### **Upload Abstracts**

#### 66<sup>th</sup> IEEE HOLM CONFERENCE

#### Hilton Palacio Del Rio San Antonio, Texas

#### 24-27<sup>th</sup> October, 2021

This is to inform you that our website is now open for accepting abstracts for the conference. To submit go to: <u>www.ieee-holm.org</u> or <u>https://www.softconf.com/l/holm21</u>

The program committee will review the abstracts at a meeting on Feb 10, 2021. Please submit your abstract by **Feb 9, 2021**. The website will guide you through the process. If you have last year's ID and password, you can use it. If you are new you will be guided through the registration. If you encounter any problems with your upload, or have a question please email Prof. Robert Jackson at the following: jacksr7@auburn.edu.

Authors will be notified on your abstract status shortly after our committee meeting.

We expect a very good conference this year and our committee looks forward to your participation in our technical program. Looking forward to seeing you in San Antonio.

Best regards,

Xin ZhouRobert JacksonConference ChairTechnical Program Chairman

**Symposium on Reliability for Electronics and Photonics Pack-aging (REPP)**—*reliability, failure modes and testing for integration of electronics and photonics (SiPh).*

#### https://attend.ieee.org/repp/

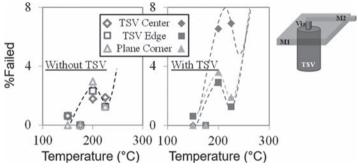

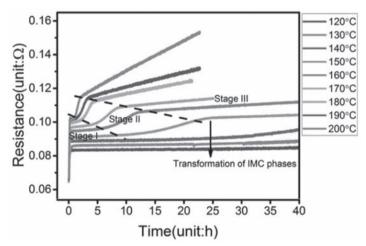

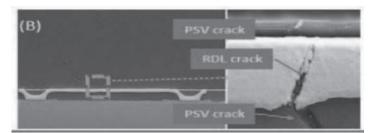

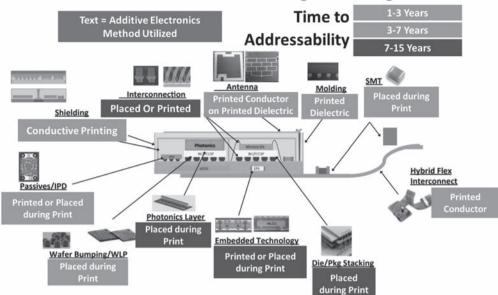

This new symposium was held virtually, from Silicon Valley on *November 12-13, 2020* with sponsorship from IEEE Silicon Valley chapter and EPS and was colead by chairs of Technical committee's of Photonics and Reliability.