JULY 2022 VOL. 44 NO. 2 ISSN 1077-2999

Driving Innovation in Microsystem Packaging /

// EPS.IEEE.ORG

#### PRESIDENT'S COLUMN

Kitty Pearsall Boss Precision. Inc. Austin, TX

Hi there!

Wow! It is mid-year 2022. The past six months have been extremely busy. Our community is transitioning from all-virtual to hybrid gatherings, and slowly back to primarily in-person meetings. ECTC, the largest EPS Flagship Conference was held in person this past June in San Diego. It felt good to network and to attend technical sessions, and keynotes. I am sure that you agree with me.

Working together we have delivered on several of our goals highlighted in the EPS Strategic Plan. Currently, I want to share a few of these with you. I believe that you too, will also be excited about our Electronic Packaging Society's achievements to date.

Our society's goals for technology are progressing extremely well. Key is positioning EPS as the preferred information source of forward-looking packaging technology. The EPS VP Technology (and his team of Technical Committee Chairs) have been collaborating closely with other technical leaders and experts to continue to provide insightful material for our newsletter, our EPS eNews, and to the EPS membership. Since January the Technology Team has published 8 technical papers in eNews. In process are an additional 9 authors preparing for the remainder of the year's papers. Many thanks to the following authors for making this possible.

- Benson Chen—"Smart Manufacturing"

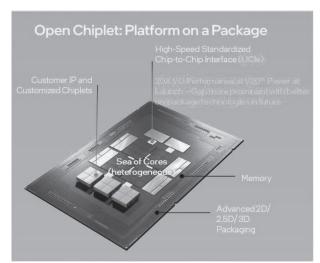

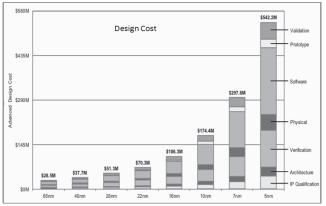

- Wendem Beyene—"Chiplets"

- Lei Sham—"The Bunch of Wires (BoW)—An Open-Source Physical Interface Enabling Chiplet Architectures"

- Patrick McCluskey and Zhaoxi Yao—"Challenges and Advances in Electric Propulsion Motor Thermal Management for Aircraft"

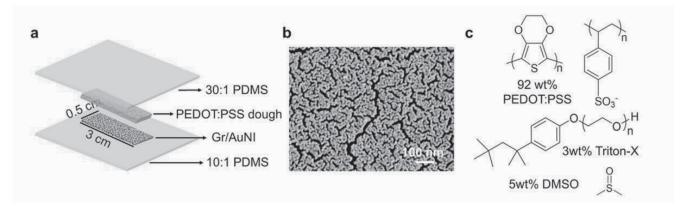

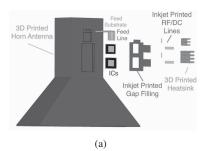

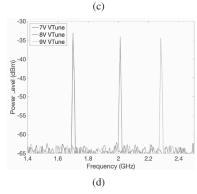

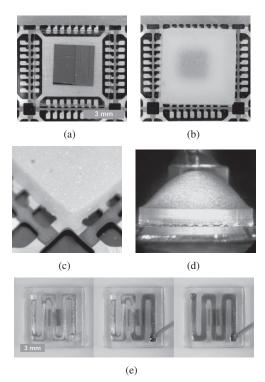

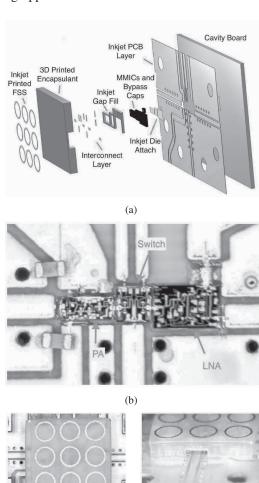

- Manos Tentzeris, Yepu Cui, and Kexin Hu—"Additively Manufactured Highly Integrated mm-Wave Packaging Structures"

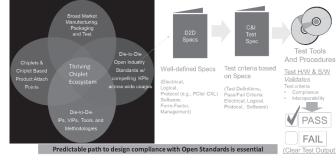

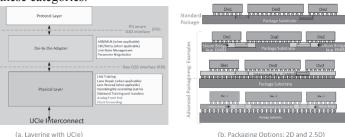

- Debendra Das Sharma—"Universal Chiplet Interconnect Express (UCIe)®: An open standard for developing a successful chiplet ecosystem"

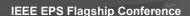

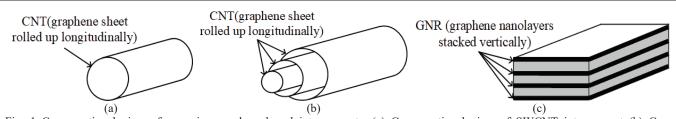

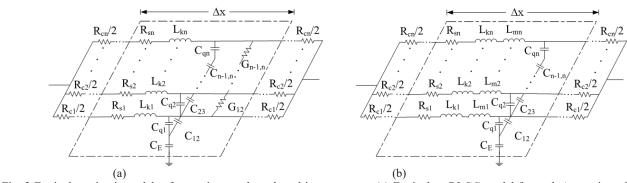

- Raj Pulugurtha—"Nano Packaging at ECTC"

- Raj Pulugurtha—"3D PEIM Invitation"

In addition to overseeing 25 plus conferences annually, our VP of Conferences and his team are paving the way for increased conferences in new locations not reached yet by EPS. Two significant examples are highlighted. First, the Design and Technology for Modern Electronic Systems (DTMES) was held in Addis Ababa, Ethiopia this year (EPS Santa Clara Valley Chapter sponsored). This was the first ever EPS conference in Africa. Second, an IEEE EPS India Workshop in collaboration with the India Electronics and Semiconductor Association Electronic Pkg is targeted for year-end in Bangalore. These new conferences present growth opportunities for our membership as well as disseminate knowledge to our community.

Per Stephen Welby, IEEE Executive Director & COO, "2022 has been a year of not just recovery, but of sustained growth". The same can be said for EPS. VP Membership reported that the membership retention YoY is 83% which is greater than the EPS strategic goal of 80%. Like IEEE, EPS also has had a positive YoY membership growth of 4.8% which is a bit more than the IEEE YoY of 3.1%. All but Regions 9 and 10 have shown an increasing retention rate for the higher-grade members.

EPS has a solid Education program that covers early professionals, mid-career, and senior engineers in the Electronics Packaging Community. Year to date there have been 24 webinars, which is in line with the 40 webinars presented in full year 2021. However, prior to 2019 the average number of webinars was 5 per year. This increase is thought to be a result of Covid putting the brakes on in-person events, workshops, and other tutorials. The sharing of chapter meetings with other chapters has been highly successful.

(continued on page 9)

# NEWSLETTER SUBMISSION DEADLINES

1 December 2022 for Winter issue 2023 15 June 2023 for Summer issue 2023

Submit all material to d.manning@ieee.org

#### **EPS Officers**

President: Kitty Pearsall, kitty.pearsall@gmail.com

VP (Technology): David McCann, david.mccann@rockleyphotonics.com VP (Conferences): Sam Karikalan, sam.karikalan@broadcom.com VP (Publications): Ravi Mahajan, ravi.v.mahajan@intel.com VP (Education): Jeff Suhling, jsuhling@auburn.edu

VP (Finance): Patrick Thompson, patrick.thompson@ti.com VP (Membership): Alan Huffman, Alan.Huffman@ieee.org Jr. Past Pres.: Chris Bailey, C.Bailey@greenwich.ac.uk

#### **Members At Large**

**2022 Term End:** Regions 1-6, 7, 9—Rozalia Beica, Xuejun Fan, Subramanian

S. Iyer, Region 8—Tanja Braun, Karlheinz Bock, Region

10— Gu-Sung Kim

2023 Term End: Regions 1-6, 7, 9—Mark Poliks, Annette Teng, Patrick

McCluskey, Jin Yang, Region 8—Steffen Kroehnert, Region

10—Yoichi Taira, Young Professional—Yan Liu

2024 Term End: Regions 1-6, 7, 9—Benson Chan, Pradeep Lall, Wolfgang

Sauter, Region 10-Kishio Yokouchi, Chuan Seng Tan, Chin-

Pin (CP) Hung

#### **Publications**

Transactions on Components, Packaging and Manufacturing Technology

Managing Editor:

Ravi Mahajan

**Co-Editor Special Topics:**

Ravi Mahajan

**Co-Editor, Electrical Performance:**

Wendem Beyene

Co-Editor, Components: Characterization and Modeling:

Koneru Ramakrishna

Co-Editor, Advanced Packaging Technologies:

Kuo-Ning Chiang

Co-Editor, Electronics Manufacturing:

Muhannad Bakir

#### **Technical Committee Chairs**

Materials & Processes:

Yi Li

**High Density Substrates & Boards:**

Takashi Hisada

Electrical Design, Modeling & Simulation:

Stefano Grivet-Talocia

Thermal & Mechanical:

SB Park

**Emerging Technology:**

Benson Chan

Nanotechnology:

Americas: Raj M. Pulugurtha, Chair; Europe: Attila Bonyar, Asia: Jian Cai

Power & Energy: Douglas Hopkins

RF & Thz Technologies:

Manos Tentzeris

Photonics—Communication, Sensing, Lighting:

Vipul Patel

3D/TSV:

Peter Ramm

Reliability:

Przemyslaw Gromala

Test:

Abram Detofsky

#### **Program Directors**

Chapter Programs: Toni Mattila, toni.mattila@investinfinland.fi

Awards Programs: Patrick McCluskey, mcclupa@umd.edu

Student Programs: Mark Poliks, mpoliks@binghamton.edu

Industry Programs: William T. Chen, William.Chen@aseus.com

Region 1-7 & 9: Annette Teng, annetteteng@promex-ind.com

Region 8 Programs: Tanja Braun, Tanja.Braun@izm.fraunhofer.de

**Standing Committee Chairs**

Fellows Evaluation: S.W. Rickly Lee, rickylee@ust.hk

Region 10 Programs: Andrew Tay, andrew\_tay@ieee.org

Long Range/Strategic Planning: Kitty Pearsall, kitty.pearsall@gmail.com

Nominations: Chris Bailey, C.Bailey@greenwich.ac.uk

# **Distinguished Lecturers**

VP Education: Jeff Suhling, jsuhling@auburn.edu

Lecturers: Ramachandra Achar, Ph.D., Mudasir Ahmad, Kemal Aygün, Ph.D., Muhannad Bakir, Ph.D., W. Dale Becker, Ph.D., Wendem Beyene, Ph.D., Karlheinz Bock, Ph.D., Bill Bottoms, Ph.D., Chris Bower, Ph.D., William T. Chen, Ph.D., Xuejun Fan, Ph.D., Philip Garrou, Ph.D., Madhu Iyengar, Ph.D., Subu Iyer, Ph.D., Beth Keser, Ph.D., Pradeep Lall, Ph.D., John H. Lau, Ph.D., Ravi Mahajan, Ph.D., James E. Morris, Ph.D., Rajen Murugan, Ph.D., Mervi Paulasto-Kröckel, Ph.D., Eric D. Perfecto, Mark Poliks, Ph.D., Gamal Refai-Ahmed, Ph.D., Jose Schutt-Aine, Ph.D., Nihal Sinnadurai, Ephraim Suhir, Ph.D., Chuan Seng Tan, Ph.D., Rao Tummala, Ph.D., E. Jan Vardaman, Paul Wesling, C.P. Wong, Ph.D., Jie Xue, Ph.D.

### **Chapters and Student Branch Chapters**

Refer to eps.ieee.org for EP Society Chapters and Student Branch Chapters list

IEEE Electronics Packaging Society Newsletter is published quarterly by the Electronics Packaging Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016-5997. US \$1.00 per member per year is included in Society fee for each member of the Electronics Packaging Society. Authors and Artists given full permission for further use of their contributions. For circulation information call IEEE Customer Service 800-701-4333, or FAX 908-981-9667.

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/ whatis/policies/p9-26.html.

$\bigoplus$

SFI Logo

JULY 2022 / IFFE ELECTRONICS PACKAGING SOCIETY NEWSLETTER

#### **EPS NEWS**

# 2022 IEEE Rao R. Tummala Electronics Packaging Award

Douglas C. H. Yu University of California, Retired Irvine, CA USA

Sponsored by IEEE Electronics Packaging Society

"For contributions to the development of advanced packaging technologies and their implementation in high-volume manufacturing."

Douglas C.H. Yu's leadership in developing advanced packaging technologies has paved the way for new technology standards and semiconductor trends that have supported the continued scaling of microelectronics and are enhancing high-performance computing, wireless, and artificial intelligence applications. Among Yu's many accomplishments, at Taiwan Semiconductor Manufacturing Corporation he led the introduction of the copper/low-k dielectric interconnects, which provided a significant improvement in on-chip wiring performance. He also led the development of the innovative TSMC 3DFabric system integration technology platform, which includes chip-on-wafer-on-substrate (CoWoS), integrated fan-out (InFO) wafer-level-package, and system-on-integrated chip (SoIC) technologies. This holistic solution for advanced packaging is critical to continued improvement in performance, power, and form factor of heterogeneous integrated microelectronic systems for above-stated wide applications.

An IEEE Fellow and a Distinguished Fellow of TSMC Academy, Yu is vice president of Taiwan Semiconductor Manufacturing Company, Hsinchu, Taiwan.

# 2022 IEEE Electronics Packaging Society Award Recipients

Charlie Zhai Apple Inc., USA 2022 IEEE EPS Electronics Manufacturing Technology Award

For his vision and industry leadership in innovating and productizing advancedpackaging technology to reshape the mobile industry.

Mukta Farooq IBM, USA 2022 IEEE EPS Outstanding Sustained Technical Contribution Award

For leadership and intellectual property in packaging technology including development and qualification of 3D logic modules and lead-free interconnect alloys.

Yueping Zhang

Nanyang Technological University

Singapore

2022 IEEE EPS Exceptional Technical

Achievement Award

For seminal contributions to the development of antenna-in-package (AiP) technology.

**Duixian Liu**IBM Thomas J. Watson Research Center, USA

# 2022 IEEE EPS Exceptional Technical Achievement Award

For seminal contributions to the development of antenna-in-package (AiP) technology.

Xiaoxiong (Kevin) Gu Metawave Corporation, USA 2022 IEEE EPS Exceptional Technical Achievement Award

For seminal contributions to the development of antenna-in-package (AiP) technology.

Chris Bailey

University of Greenwich, United Kingdom

2022 IEEE EPS David Feldman Out-

standing Contribution Award

For outstanding service and technical leadership to the Electronics Packaging Society resulting in the growth and relevancy of

resulting in the growth and relevancy of EPS in a fast-changing electronic packaging landscape.

Fumihiro Inoue

Yokohama National University, Japan **2022 Outstanding Young Engineer Award** For groundbreaking contributions to the development of 3D integration, including electro/electroless deposition, extreme Si thinning, wafer bonding and singulation process.

#### **Rolf Aschenbrenner**

Fraunhofer Institute for Reliability and Microintegration (IZM), Germany

2022 IEEE EPS Regional Contributions Award—Region 8 (Europe, Middle East and Africa)

For outstanding accomplishments in the development of new interconnect technologies for single chip packaging, as well as in

various areas of 3D IC integration and 3D Packaging.

Peng Zhao

Nanyang Technological University, Singapore Institute of Microelectronics (A\*STAR), Singapore

2022 PhD Fellowship

For contributions to 3D packaging of trapped ion devices for application in quantum information processing.

Masahiro Aoyagi

Kumamoto University, Japan 2022 IEEE EPS Regional Contributions Award—Region 10 (Asia & Pacific)

For contribution to enhance collaboration in Region 10, especially between Japan and Singapore and achievement to develop 3D LSI chip stacking technology with TSVs and micro-bumps.

### Rajen Murugan

Texas Instruments, Inc., USA

2022 IEEE EPS Regional Contributions

Award—Regions 1 – 7 & 9 (Americas)

For founding the EPS Dallas Chapter

and demonstrating exemplary leadership

and sustained technical contributions in

enabling and promoting EPS and IEEE programs and activities in the Dallas Section

and Region 5.

# Chris Bailey 2022 EurosimE Award Receipent

Chris Bailey, EPS Jr. Past President, received the EurosimE 2022 Achievement Award "for his outstanding contributions to thermal and multi-physics simulation and experiments in microsystems as well as research on various industrial applications."

# Congratulations to IEEE EPS Senior Members New IEEE EPS Senior Members

he members listed below were elevated to the grade of Senior Member between December 2021 and April 2022. The grade of Senior Member is the highest for which application may be made and shall require experience reflecting professional maturity. For admission or transfer to the grade of Senior Member, a candidate shall be an engineer, scientist, educator, technical executive, or originator in IEEE designated fields for a total of 10 years and have demonstrated 5 years of significant performance.

For additional information or to apply online: https://www.ieee.org/membership/senior/

David Armstrong, Denver Section

Koushik Banerjee, Phoenix Section

Anandaroop Bhattacharya, Kharagpur Section

Hua Chen, Guangzhou Section

Vasiliki Giagka, Benelux Section

Blake Gray, Atlanta Section

Zhang Ju Hou, Guangzhou Section

Kenji Okada, Kansai Section

James Petroski, Cleveland Section

Herbert Stopper, Florida West Coast Section

Bruce Weiss, Milwaukee Section

Tiong Leh Yap, Singapore Section

Tianchun Ye, Beijing Section

4

#### **ECTC 2022 Travel Award Winners**

ongratulations to the winners of the 2022 ECTC travel award. The award is intended to assist students to attend ECTC.

Ramesh Kudalippalliyalil

Information Sciences Institute

(ISI/USC)

**UCLA ECE** Yu-Tao Yang

Zeinab Shaban

Akeeb Hassan

Peng Zhao

Tyndall National Institute, University College, Cork Florida International University Nanyang Technological University

Binghamton University

Firas Alshatnawi Yi Zhou Georgia Tech Xiaofan Jia Georgia Tech Kruitkesh Sahoo **UCLA**

Woosol Lee University of Florida

# Congratulations to the ECTC Volunteer **Award Recipients**

he EPS/ECTC Volunteer Award is given to those individuals who contribute to the success of the ECTC by volunteering in one of the conference committees, year after year. Here are the 2022 EPS/ECTC Volunteer Award winners:

10 year Volunteers

Kemal Aygun Tz-Cheng Chiu Gordon Elger Jae-Woong Nah Valerie Oberson Dan Oh

P. Markondeya Raj Katsuyuki Sakuma Dwayne Shirley Ivan Shubin Yoichi Taira

# **EPS Major Awards Nomination Period Starts on** September 15

Il the EPS Major Award nominations will require line submission. The nomination period to input all the required documents runs from September 15 to January 21. The Electronics Packaging Society offers the following awards for the purpose of recognizing outstanding service and contributions to furthering the professional purposes of IEEE and EP Society.

Outstanding Sustained Technical Contributions Award: To recognize outstanding sustained and continuing contributions to the technology in fields encompassed by the EP Society.

Prize: \$3,000 and Certificate

Basis for Judging: Technical contributions must be sustained and continuing over a period of at least 15 and preferably 20 years. One major contribution will not qualify. Must be documented by open literature publications such as papers, patents, books and reports (available to the public).

Eligibility: Must have been a member of the IEEE and EP Society for the past three (3) years (2020–2022), and renewed for 2023.

Electronics Manufacturing Technology Award: To recognize major contributions to Electronic Manufacturing Technology in fields encompassed by the EP Society.

Prize: \$3,000 and Certificate

Basis for Judging: Contributions may include technical development of, or management (directing) of major new electronic manufacturing processes; significantly increasing yield and/or reliability of established manufacturing processes, etc. Contributions must be sustained and continuing over a period of at least 15 and preferably 20 years. Work in the management of EPS Conferences or its BoG may be contributory, but it is not a requirement

Eligibility: No need to be a member of IEEE and EP Society.

IEEE William Chen Distinguished Service Award: To recognize and honor outstanding service and leadership to the Electronics Packaging Society and its sponsored activities.

Prize: US\$5,000 and Certificate

Basis for Judging: Recipient is required to have made outstanding contributions to expanding the Society's impact in the electronic packaging field and profession through service and leadership within the EPS organization, including activities at the Chapter, Regional or BoG level or through the society's primary conferences and workshops. Examples would include serving as a conference chair, society officer, regional director, etc.

Eligibility: At the time of nomination, the nominee must have been continuously a member for the previous ten (10) years of IEEE and EPS with respect to the year of presentation of the award, and have already renewed the membership for the year of presentation of the award.

Exceptional Technical Achievement Award: To recognize an individual, or group of individuals (no more than three), for exceptional technical achievement in the fields encompassed by the EP Society.

Prize: \$2,500 and a Certificate.

**Basis for Judging**: Technical contributions of the nominee(s) must be such that they are considered to be exceptional, not achieved by most members. A single major contribution will qualify for this award. The contribution could be a significant invention, introduction

of a significantly new and important technology or product (in which case, the nominee may be a team leader), or significant work that advances the state-of-the-art in EPS's field of interest. The technical contributions must be documented by open literature publications such as papers, patents, books, and reports (available to the public). Technical recognition and awards from the organization employing the individual as well as awards from other IEEE and non-IEEE technical societies may also be contributory.

**Eligibility**: Recipient(s) must have been a member of IEEE and EPS for the past three (3) years (2020–2022), and renewed for 2023. There are no requirements for service to the IEEE or EP Society.

**Outstanding Young Engineer Award:** To recognize outstanding contributions to the fields encompassed by the EP Society through invention, technical development, publications, or new product implementation.

Prize: \$1,500 and Certificate

Basis for Judging: Technical contributions through patent invention, contributions to technology or product development within the EPS Field of Interest. May encompass management (directing) of significant new product introduction or implementation of major new electronic manufacturing processes; significantly increasing yield and/or reliability of established manufacturing processes. Contributions to the Society, through the BoG, Conferences, Chapters, etc., will also be considered. Proof of contributions may consist of open literature publications (preferred) such as papers, patents, books, and reports (available to the public). At least three (3) letters from peers and management at the nominee's place of employment attesting to the accomplishment(s) can be accepted in lieu of publications.

**Eligibility**: Must have been a member of the IEEE and EPS (member grade or above) for the past three (3) years (2020–2022), and renewed for 2023, and must be 35 years of age, or younger, on December 31, 2023.

**Regional Contributions Award:** To recognize significant and outstanding leadership and contributions to the growth and impact of EPS programs and activities at the Region level. Maximum of one award annually from each Region/ Groups of Regions (3 awards): Regions 1-7 & 9; Region 8; and Region 10.

**Basis for Judging**: Demonstrated service and leadership in areas that may include but are not limited to Chapter activities, Conference/Workshop activities, Membership Development, Student Programs and Technical Activities. The respective EPS Regional Advisory Committees will receive nominations, evaluate candidates, select a candidate(s), and present candidate(s) to EPS Awards Committee for review and approval.

**Eligibility**: Recipient(s) must have been a member of IEEE and EPS for the past three (3) years (2020–2022), and renewed for 2023.

#### **Guidelines for Nominators:**

A recipient of any EPS Major Award will be eligible for nomination for another EPS Major Award after two award cycles have passed. (i.e., Recipient of XX Award in 2020 becomes

- eligible for nomination for YY Award in 2023). For lists of past awardees, see http://eps.ieee.org/awards.html

- Past recipients of an award are not eligible to receive that same award. For lists of past awardees, see http://eps.ieee.org/ awards.html

- An individual may submit only one nomination per award but may submit nominations for more than one award.

- An individual may submit only one endorsement per award but may submit endorsement for more than one award.

- It is the responsibility of the nominator to ensure quality documentation to assist the Awards Committee in evaluating the candidate.

- Outstanding Sustained Technical Contribution Award is designed for the "practitioner", while the Electronics Manufacturing Technology Award intended for "Corporate Leadership".

- Complimentary material, such as candidate's picture, CV, list

of publications and/or patents should be submitted separate

from the award nomination.

- Self-nominations will not be considered.

#### **EPS PhD Fellowship:**

To promote, recognize, and support PhD level study and research within the Electronics Packaging Society's field of interest.

**Prize:** A plaque and a single annual award of US\$5,000, applicable towards the student's research.

**Basis for Judging:** Demonstration of his/her significant ability to perform independent research in the fields of electronic packaging and a proven history of academic excellence, as documented in:

- Nomination by an IEEE EPS Member. Only one nomination per member per year.

- Two-page (maximum) statement by the student describing his or her education and

- Research interests, accomplishments, and impact on the electronics package industry.

- Proof of contributions to the community may consist of open literature publications (preferred) such as papers, patents, books, and conference presentations and reports (available to the public).

- At least one letter of recommendation from someone familiar with the student's work

- Student resume

**Eligibility**: Candidate must be an IEEE EPS member, at the time of nomination, and be pursuing a doctorate degree within the EPS field of interest on a full-time basis from an accredited graduate school or institution. The candidate must have studied with her/ his advisor for at least 1 year, at the time of nomination, to be eligible. A Student who received a Fellowship award from another IEEE Society, within the same year, or is a previous EPS Fellowship winner is ineligible.

All Award nominations must be **online.** Nominations questions can be sent to the Society Awards Program director:

Patrick McCluskey mcclupa@umd.edu

Winners will be notified by April 2023, and the awards will be presented at the 73rd Electronic Components and Technology Conference (ECTC). **Date and venue will be announced when determined.**

#### **MEMBERSHIP NEWS**

### **NEW—Society Member Digital Library**

Beginning with the 2023 renewal cycle, EPS members will have access to the new EPS Society Digital Library!

This will include online access via Xplore to the Transactions on Components, Packaging and Manufacturing Technology (T-CPMT), EPS sponsored conference proceedings including ECTC, ESTC, ITherm and more!

Unlimited access to current and past issues of T-CPMT and proceedings for EPS sponsored conferences from current year to the early nineties.

# **IEEE Senior Membership: Are You In?**

If you have been involved in the electronics packaging field for 10 years or more, chances are that you probably already have the necessary qualifications to be an IEEE Senior Member. Senior membership is the highest IEEE membership grade that can be applied for and is a recognition of sustained and significant performance in an IEEE-designated field. Individuals who are IEEE members can apply themselves for elevation to Senior Member or they can be nominated by others. Since a member can be nominated by someone else for Senior Membership, Society Chapters can play an important role in helping to identify and support applications for elevation. Nominating individuals in our Chapters is a great way to recognize their professional achievements and foster deeper personal and professional relationships with our peers. Individual members shouldn't hesitate to apply for Senior Member elevation on their own as well, and call upon their IEEE colleagues for support for their application. The requirements for Senior Member eligibility are very straightforward:

- The candidate shall be an engineer, scientist, educator, technical executive, or originator in IEEE-designated fields

- Candidates shall have been in professional practice for at least ten years

- Candidates shall have shown significant performance over a period of at least five of those years

As a member of EPS, the IEEE-designated field criteria will generally have been met. The criteria for ten years of professional practice can also take into account some portion of your educational experience as well as time spent in one's job or career, so a ten-year employment record isn't necessarily required. The

final criteria of demonstrating significant performance over at least five of those ten years can be met in many different ways, including technical work, managerial responsibility, and publications to name a few. IEEE provides detailed information on the requirements for Senior Member grade at <a href="https://www.ieee.org/membership/senior/senior-requirements.html">https://www.ieee.org/membership/senior/senior-requirements.html</a>, along with sample cases that can be helpful for comparison to your own professional experiences.

Individuals applying for or nominating someone for Senior Member elevation can find additional information on the IEEE website at <a href="https://www.ieee.org/membership/grade-elevation.html">https://www.ieee.org/membership/grade-elevation.html</a> and clicking on the Senior Member Grade link found there. Candidates applying for Senior Membership will need to supply three references from current IEEE members who are Fellows, Senior Members, or Honorary Members, and this is where EPS colleagues can support one another. Members of EPS chapters already have a group of local contacts that can help with nomination and reference support, simplifying and streamlining the process. Prospective applicants can find potential references through IEEE Collabratec via a link at the top of the EPS Membership page. There is also a link to the general Collabratec page on the MGA Senior Member Requirements page.

IEEE Senior Membership is a way for the Society to recognize the dedication and achievements of our members as well as a way to support our colleagues. If you have any questions about the Senior Membership application process or requirements, please don't hesitate to reach out to your local chapter or to us here at EPS for assistance.

Thanks Alan Huffman, EPS VP Membership

#### **PUBLICATIONS NEWS**

#### **2021 CPMT Best Transactions Paper Awards**

ach year, the Editors of the IEEE Transactions on Components, Packaging and Manufacturing Technology select the best papers published in the prior year. The papers are selected from among over 200 published papers and represent the best, based on criteria including originality, significance, completeness and organization.

Subscribers to this publication can access the papers on-line in IEEE Xplore at: http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=5503870

#### **Advanced Packaging Technologies Category**

"Fan-Out Panel-Level Packaging of Mini-LED RGB Display" John H. Lau; Cheng-Ta Ko; Curry Lin; Tzvy-Jang Tseng; Kai-Ming Yang; Tim Xia; Puru Bruce Lin; Chia-Yu Peng; Eagle Lin; Leo Chang; Ning Liu; Show May Chiu; Tzu Nien Lee; Volume 11, Issue 5, May 2021

#### **Abstract:**

In this study, the feasibility of mini-light-emitting diode (LED) RGB display fabricated by a chip-first fan-out panel-level packaging is investigated. Emphasis is placed on the design, materials, process, fabrication, and reliability of the mini-LED RGB display package on a printed circuit board (PCB). The mini-LEDs under consideration and their sizes are red ( $125 \times 250 \times 100 \,\mu\text{m}$ ), green  $(130 \times 270 \times 100 \,\mu\text{m})$ , and blue  $(130 \times 270 \times 100 \,\mu\text{m})$ . The spacing among the RGB mini-LEDs is 80 µm, the pixel-to-pixel spacing is also  $\sim 80 \, \mu m$ , and the pixel pitch is 625  $\mu m$ . The temporary glass panel for making the redistribution layers (RDLs) of the package is  $515 \times 510 \times 1.1$  mm in size. To increase the SMT assembly yield on the PCB, the mini-LEDs are grouped into  $4(2 \times 2 \text{ pixels})$ -inone surface mount device (SMD), that is, a total of 12 R, B, and G mini-LEDs. A PCB (132 mm × 77 mm) is designed and fabricated for the drop test of the mini-LED package. Thermal cycling of the mini-LED SMD PCB assembly is also performed by a nonlinear temperature- and time-dependent finite-element simulation.

URL: https://ieeexplore.ieee.org/document/9393937

#### **Components: Characterization and Modeling Category**

"Cascaded Multi-Core Vapor Chambers for Intra-Package Spreading of High Power, Heterogeneous Heat Loads" Soumya Bandyopadhyay; Amy M. Marconnet; Justin A. Weibel; Volume 11, Issue 6, June 2021

#### **Abstract:**

A cascaded multicore vapor chamber (CMVC) is designed for dissipating heat from high-flux hotspots simultaneously with a high-total-power background. Current thermal management strategies rely on spreading high local heat fluxes by conduction in the lid of electronics packages. Embedding vapor chambers (VCs) within the lid is an attractive option to directly address intrapackage hotspots. We investigate the design of intralid VCs, for a generic

device having a total heat load of 476 W having a background heat flux of 0.75 W/mm 2, with hotspots of 8 W/mm 2 over a 1-mm 2 area. A conventional VC design, having a single vapor core, will require a thick evaporator wick to avoid the capillary limit for large total power. The necessity for a thick wick then imposes a large thermal conduction resistance when the VC is exposed to high heat flux hotspots. The proposed CMVC architecture aims to address this limitation. The cascaded architecture comprises a bottom-tier VC having an array of multiple small vapor cores for spreading heat from the small hotspots. These small vapor cores have short paths of liquid return to the evaporator, such that they can handle their footprint heat load while using thin wicks, resulting in a low hotspot thermal resistance. Furthermore, local dampening of the hotspots by the bottom tier then reduces the thermal conduction resistance across the necessarily thick wick in the top tier. Hence, the cascaded architecture has the potential to significantly reduce the overall thermal resistance, relative to a single tier. To substantiate this design rationale, experiments are performed to illustrate that the resistance of a commercial VC can be significantly reduced by interfacing the heat source with an intermediate heat spreader. Reduced-order models are then used to understand the effect of the wick properties (porosity and particle size) and geometric parameters on the thermal performance of the CMVC for the representative power map. The optimal CMVC design offers a thermal resistance (0.66 K/W) that is significantly lower compared to a conventional single-core VC (1.76 K/W) owing to a reduction in the conduction resistances across the internal wicks. That parametric optimization results demonstrate that the thermal resistance of the CMVC is more sensitive to the wick porosity compared to the particle diameter. Furthermore, there exists a wide range of wick properties and vapor core sizes for which near-optimum thermal performance can be attained, which is particularly attractive from the standpoint of flexibility in design and manufacturing.

URL: https://ieeexplore.ieee.org/document/9391679

# **Electronics Manufacturing Category:**

2021 "Towards 224Gb/s Electrical Signaling – Modulation, Equalization and Channel Options" Masum Hossain; Wendemagegnehu T. Beyene; Volume 11, Issue 3, March 2021

#### **Abstract:**

This article explores different modulation and signaling techniques with the goal to achieve 224-Gb/s link speed through electrical signaling. Focus of this work spans from interconnects to transceiver architecture from system and signaling point of view. In addition to traditional multilevel signaling pulse amplitude modulation-4 (PAM-4 and PAM-8), this work also compares simultaneous bidirectional signaling and multiwire encoding techniques as potential solutions beyond 224-Gb/s link. These signaling options are compared both from performance and implementation complexity point of view with possible improvements required to further extend the speed and reach of electrical signaling.

URL: https://ieeexplore.ieee.org/document/9336667

#### **Best Associate Editor Award**

To recognize the work and efforts of our Associate Editors, EPS instituted the Best Associate Editor Award. The 2022 recipients are:

Lavanya Aryasomayajula—Intel Yogendra K. Joshi—Georgia Institute of Technology Xiaoxiong (Kevin) Gu-Metawave Corporation

# **Most Popular Articles according** to Xplore® usage statistics

#### Recent Advances and Trends in Advanced Packaging

John H. Lau

Publication Year: 2022, Page(s): 228-252

# CPU Overclocking: A Performance Assessment of Air, Cold Plates, and Two-Phase Immersion Cooling

Bharath Ramakrishnan; Husam Alissa; Ioannis Manousakis; Robert Lankston; Ricardo Bianchini; Washington Kim; Rich Baca; Pulkit A. Misra; Inigo Goiri; Majid Jalili; Ashish Raniwala; Brijesh Warrier; Mark Monroe; Christian Belady; Mark

Shaw; Marcus Fontoura

Publication Year: 2021, Page(s): 1703–1715

#### A Review of 5G Front-End Systems Package Integration

Atom O. Watanabe; Muhammad Ali; Sk Yeahia Been Sayeed; Rao

R. Tummala; Markondeya Raj Pulugurtha Publication Year: 2021, Page(s): 118–133

# Thermal and Mechanical Characterization of 2.5-D and Fan-Out Chip on Substrate Chip-First and Chip-Last Packages

Meng-Kai Shih; Weihong Lai; Tsewei Liao; Karen Chen; Dao-

Long Chen; C. P. Hung

Publication Year: 2022, Page(s): 297-305

### A Review of Recent Research on Heat Transfer in Three-**Dimensional Integrated Circuits (3-D ICs)**

Swapnil S. Salvi; Ankur Jain

Publication Year: 2021, Page(s): 802–821

# **President's Column** (Continued from page 1)

The Professional Development Courses offering IEEE Continuing Educational Units has been extended to include EurosimE in addition to the EPS Flagship Conferences.

Finally, through IEEE Xplore you have access to peer-reviewed journals, refereed papers from conference proceedings, and conference presentations. In addition, the EPS VP of Publications is developing a strategy to support the IEEE's Open Access (Multidisciplinary Open Access Journal) work effort.

Looking forward I want to increase our focus on EPS partnering with JIEP and the India Electronics and Semiconductor Association. Coming challenges for the next 18 months for EPS are Digitization, Artificial Intelligence, IOT, and Smart Manufacturing, how and where this fits in the EPS Strategic plan.

Lastly, I want to express my gratitude for the dedicated support provided to the EPS Board of Governors from all VPs, Directors, Members at large, Adhoc Leaders, volunteers, and appointees. I consider myself lucky to be supported by every one of you.

- Dave McCann, VP Technology

- Sam Karikalan, VP Conferences

- Ravi Mahajan, VP Publications and India Initiative Lead

- Jeff Suhling, VP Education

- Alan Huffman, VP Membership

- Pat Thompson, VP Finance

- Chris Bailey, Jr. Past President

- Toni Matilla, Director of Chapters

- Bill Chen, Director of Industry Programs

- Mark Poliks, Director of Student Programs

- Patrick McCluskey, Director of Awards

- Annette Teng, Director of Regions 1-7 & 9

- Tanja Braun, Director of Region 8

- Andrew Tay, Director of Region 10

- Members at Large and Adhoc Leads

- Regions 1-7 and 9—Xuejun Fan, Subu Iyer, Rozalia Beica, Patrick McCluskey, Mark Poliks, Annette Teng, Jin Yang, Benson Chan, Pradeep Lall and Wolfgang Sauter

- Region 8—Karlheinz Bock, Tanja Braun, and Steffan Kroehnert

- Region 10—Gu-Sung Kim, Yoichi Taira, Chih-Pin Hung, Chuan-Seng Tan, and Kishio Yokouchi.

- Yan Liu—Young Professionals

- Marta Rencz—Women in Engineering representative.

- Ricky Lee—Fellows Evaluation Chair

- Yasumitsu Orii—Partnering with outside organizations

- Pradeep Lall—Partnering with IEEE Societies

Kitty Pearsall

# **EDUCATION/CAREER NEWS**

#### **EPS Achievement Certificate**

**Congratulations** to these EPS Members on receiving the IEEE Achievement Certificate from the IEEE Electronics Packaging Society and completing the required number of professional development hours.

Ken Lawrence, CAES Stoyan Stoyanov, University of Greenwich Sreejith Kochupurackal Rajan, Georgia Institute of Technology

#### Nikhilendu Tiwary, Aalto University

Congratulations to these EPS Members on receiving the IEEE Certificate of Distinguished Achievement from the IEEE Electronics Packaging Society and completing the required number of professional development hours.

**Chong Leong Gan**, Micron Memory Taiwan Co. Ltd. **Scott Clary**, Florida Institute of Technology

#### **EPS Distinguished Lecturer Program**

PS Distinguished Lecturers are selected from among EPS Fellows, Award winners, and Society leaders, who are members of the technical community and experts in their field. They are available to present lectures and/or courses at EPS events—Chapters, Conferences, Workshops or Symposia; as well as IEEE Student Chapter events.

The EPS Distinguished Lecturer Program (DLP) aims at serving communities interested in the scientific, engineering, and production aspects of materials, component parts, modules, hybrids and micro-electronic systems for all electronic applications.

The Program strives to support EPS Chapters worldwide by helping them to invite leading researchers in their respective fields and IEEE Student Chapters to encourage students to pursue EPS related fields and to join the EPS society. The DLP talk is a major event in the life of the inviting Chapter.

#### **EPS Distinguished Lecturers**

**Ramachandra Achar**, Ph.D. (7/1/2020–6/30/2024)

Department of Electronics, Carleton University

Ottawa, Ontario, CANADA

**Topics**: CAD tools and methodologies for interconnects, packages, and systems with an emphasis on signal, power and EMI integrity

**Mudasir Ahmad** (1/2022–12/2025)

Google

CA, USA

**Topics**: Internet of Things (IoT), Advanced Packaging, 2.5D, Heterogeneous Silicon Photonics, Advanced Reliability (Thermomechanical, Mechanical Shock), Numerical Modeling, Advanced Thermal Solutions, Stochastic Analysis, Bayesian Inference, Machine Learning, Artificial Intelligence

**Kemal Aygün**, Ph.D. (7/1/2020–6/30/2024)

**Intel Corporation**

Chandler, AZ USA

**Topics**: Package/socket/board/interconnect technologies, electrical simulation methodology and lab metrologies

Muhannad Bakir, Ph.D. (1/2020–1/2024)

School of Electrical and Computer Engineering

Georgia Institute of Technology

Atlanta, GA USA

**Topics**: Emerging interconnection architectures and technologies; heterogeneous system design and integration

**W. Dale Becker**, Ph.D. (7/1/2020–6/30/2024)

**IBM**

Poughkeepsie, NY USA

**Topics**: Electronic Package design and integration, system design, electrical modeling tools

Wendem Beyene, Ph.D. (7/1/2020-6/30/2024)

Meta

San Jose, CA

**Topics**: Electrical modeling and simulation techniques for analysis of interconnects, packages, and systems. Machine learning techniques

**Karlheinz Bock**, Ph.D. (7/2020–7/2024)

Technische Universität Dresden

Dresden, Germany

**Topics:** Multifunctionality & heterosystemintegration & additive manufacturing (IoT, Industry 4.0, tactile internet), packaging for mechanical, digital and power co-integration (automotive, machines, robots..), 2.5D and 3D electro-optical-RF interposer and board (high performance), heterointegration for flexible, bio, organic and large area electronics (open form factor)

Bill Bottoms, Ph.D. (6/2021–6/2025)

Third Millennium Test Solutions

Santa Clara, CA USA

**Topics**: Heterogeneous Integration, Semiconductor test technology, Emerging research materials, Packaging of electronic components and systems, the global network and its future requirements, the internet of things and Smart manufacturing

Chris Bower, Ph.D. (6/2021–6/2025)

X-Celeprint Inc.

North Carolina, USA

10

**Topics**: novel assembly methods, elastomer stamp micro-transfer-printing, heterogeneous integration, three-dimensional integration, manufacturing of micro-assembled displays and other large-format electronics.

#### William T. Chen, Ph.D. (1/2020–1/2024)

ASE (U.S.) INC

Santa Clara, CA USA

Topics: Semiconductor and Electronics Industry Trends and

Roadmap

#### **Xuejun Fan**, Ph.D. (1/2020–1/2024)

Department of Mechanical Engineering

Lamar University Beaumont TX USA

**Topics**: Design, modeling and reliability in micro-/nano- electronic packaging and microsystems

trome packaging and interosystems

#### **Philip Garrou**, Ph.D. (1/2020–1/2024)

Microelectronic Consultants of North Carolina

Research Triangle Park, NC USA

Topics: Thin film technology; IC packaging and interconnect;

Microelectronic materials; 3D-IC integration

#### **Madhu Iyengar**, Ph.D. (7/1/2020–6/30/2024)

Google

Mountain View, CA

Topics: Thermal component and system design for packages,

servers, and data centers.

#### **Subu Iyer**, Ph.D. (6/2021–6/2025)

University of California, Los Angeles

Los Angeles, CA USA

Topics: Heterogeneous Integration; Flexible hybrid electronics;

3D interposer, and wafer scale integration and stacking

#### **Beth Keser**, Ph.D. (1/2020–1/2024)

Intel

San Diego, CA USA

**Topics**: Fan-Out Wafer Level Packaging and Wafer Level Packaging structures; processes, materials, tools, design rules and

roadmaps; photoimageable liquid polymer films

#### **Pradeep Lall**, Ph.D. (1/2020–1/2024)

Auburn University

Auburn, AL, USA

**Topics**: Semiconductor Packaging, Modeling and Simulation, Reliability in Harsh Environments, Shock/Drop/Vibration, Cu Wirebonding, Flexible Hybrid Electronics, Additive Manufacturing, Prognostics and Health Management, LEDs, Micro CT Measurements

### John H. Lau, Ph.D. (1/2020–1/2024)

ASM Pacific Technology

Hong Kong

Topics: Electronics and Photonics 2D and 3D packaging and

manufacturing

#### Ravi Mahajan, Ph.D. (7/2020–7/2024)

Intel Corporation

Arizona, USA

Topics: Advanced Packaging Architectures, Assembly Processes

and Thermal Management

#### **James E. Morris**, Ph.D. (1/2020–1/2024)

Department of Electrical and Computer Engineering

Portland State University

Portland, Oregon USA

Topics: Electrically conductive adhesives; Electronics packaging;

Nanotechnologies

# **Rajen Muguran**, Ph.D. (7/2022–7/2026)

Texas Instruments

Dallas, TX, USA

**Topics:** Multiphysics and System Co-Design modeling for complex analog and mixed-signal packaging, mmWave/THz signal integrity, power electronics packaging, and System-Level EMI/EMC modeling, analysis, and characterization.

### Mervi Paulasto-Kröckel, Ph.D. (7/2020–7/2024)

Aalto University

Helsinki, Finland

**Topics**: MEMS, electronics reliability, automotive components and packaging, implantable electronics, dissimilar materials & interfaces

#### Eric D. Perfecto, (1/2020–1/2024)

IBM Research

Poughkeepsie, NY USA

**Topics**: Fine pitch interconnect, chip to chip and chip to laminate connection, UBM and solder selection, chip package interaction and 2.5D fabrication

#### Mark Poliks, Ph.D. (1/2020 – 1/2024)

Binghamton University (SUNY)

Binghamton, NY USA

**Topics**: Materials and Processes, Advanced Manufacturing, Flexible Hybrid Electronics, High Speed and Additive

Gamal Refai-Ahmed, Ph.D. (7/1/2022-6/30/2026)

Xilinx

$\bigoplus$

San Jose, CA, USA

**Topics**: Thermo-mechanical Semiconductor and Electronics Industry Roadmap and directions, Advanced holistic Thermo-mechanical solution, assembly and reliability of Heterogeneous Packaging and Silicon Photonics, Future thermo-mechanical technology, architecture for component and system

#### Jose Schutt-Aine, Ph.D. (1/2020–1/2024)

University of Illinois

Champaign, IL, USA

**Topics**: High-Frequency Measurements, Mixed-Signal Design, High-Performance Computing, electromagnetic Modeling, Signal Integrity, CAD Tools for Interconnects and Packages, Machine Learning for High-Speed System Modeling

#### Nihal Sinnadurai (1/2020–1/2024)

Suffolk IP11 9RZ UK

**Topics**: Accelerated Ageing for Reliability Assurance-theory and practical methods-including HAST (my invention originally); The use of encapsulation and plastic packaging and reliability evaluation method; PCB & Hybrid technologies; Thermal management and design

#### **Ephraim Suhir**, Ph.D. (1/2020–1/2024)

Los Altos, CA 94024 USA

Topics: Accelerated life testing; Probabilistic physical design for reliability; Bonded assemblies; Thermal stress; Predictive modeling; Fiber optics structures: design for reliability; Dynamic response to shocks and vibrations

#### **Chuan Seng Tan**, Ph.D. (6/2019–6/2023)

Nanyang Technologica University

Singapore

Topics: 3D Integration and packaging, Fine Pitch Cu-Cu Bonding Through Silicon Vias (TSVs), Group IV Semiconductors: Material Growth, Engineered Substrates, and Device Applications

#### **Rao Tummala**, Ph.D. (1/2020–1/2024)

Microsystems Packaging Research Center (PRC)

Georgia Institute of Technology

Atlanta, GA USA

Topics: Electronics Packaging

#### E. Jan Vardaman (1/2020–1/2024)

TechSearch International, Inc.

Austin, TX USA

Topics: International developments in semiconductor packaging, manufacturing and assembly; SiP: Business and technology Trends; drivers in advanced packaging; Flip chip and wafer level packaging

#### **Paul Wesling** (1/2020–1/2024)

Saratoga, CA USA

Topics: Origins of Silicon Valley and the Electronics Packaging Society; the IEEE/SEMI/ASME Heterogeneous Integration Roadmap and how to use it (as editor for the 2019 Roadmap).

#### **C.P. Wong**, Ph.D. (1/2020–1/2024)

Georgia Institute of Technology

Atlanta, GA, USA **Topics**: Materials

**Jie Xue**, Ph.D. (1/2020–1/2024)

Cisco Systems, Inc

San Jose, CA, USA

Topics: Advanced Packaging for Networking Application; Impact of Internet of Everything (IoE) to Semiconductor Industry ecosystem; High performance substrate technologies; Trends and challenges of Silicon Photonics for datacenter and networking applications

# **EPS Certificate Program**

he IEEE Electronics Packaging Society Certificate Program provides a pathway for early and mid to late-career professionals to highlight their accomplishments.

Criteria for all Certificates: Must be an IEEE Electronics Packaging Society Member.

There are three Certificates you may apply for, which are noted below.

# **EPS Achievement Certificate**

The first level EPS Achievement Certificate is aimed at earlycareer professionals working in the field of electronics packaging.

It is especially intended to encourage the career development of young professionals including advanced graduate students.

Criteria: Current EPS Member

To receive your certificate, 15 professional development hours (PDHs) must be completed. This can be obtained from a combination of the following:

- 1) IEEE EPS Webinar (1 PDH)—must complete **PDH evaluation**.

- 2) Professional Development Courses—must complete survey and CEU credit form. Previous ECTC PDCs from the last 10 years can be used towards this if the CEU application was completed at the time of the course. PDCs from ESTC and EPTC 2018 and forward can be used.

- Electronic Components and Technology Conference (USA)

4 PDHs

- Electronic Systems-Integration Technology Conference (Europe) = 3 PDHs

- o Electronic Packaging Technology Conference (Asia) = 4 PDHs

- 3) Author of IEEE T-CPMT and/or EPS conference paper(s) (5 PDHs)—paper must be published in IEEE Xplore within the last 5 years.

- 4) Reviewer for IEEE T-CPMT (3 Reviews = 5 PDH) within the last 5 years.

Once you have completed any combination of the above and received 15 PDHs, please complete the certificate form to request your Electronics Packaging Society Certificate of Achievement.

# **EPS Distinguished Achievement Certificate** for Technical Leadership and Expertise

Criteria: Must be a current EPS member

There are five high-level focus areas for this new certificate. These areas include:

Being a recognized authority of technical expertise in one's field.

Being a recognized authority of technical expertise in electronics packaging. Examples include being an advanced member of the technical staff at a company (e.g. Fellow, Senior Technical Staff, Distinguished Engineer, etc.), making technical contributions as a

Member or Fellow of professional associations/societies related to electronics packaging (e.g., IEEE, IMAPs, SMTA, ASME, etc.), and being an invited speaker at companies, technical conferences, and EPS Chapter meetings.

2) Being a subject matter expert (SME) in electronics packaging at conferences, keynotes, webinars, blogs.

Methods to demonstrate participation as a SME include abstracts accepted and papers presented at conferences, giving keynote lectures at conferences or professional society meetings, presenting webinars for EPS and other IEEE Societies, and serving on technical panels at conferences and other venues.

3) Demonstrating sustained technical contributions to the electronics packaging.

Demonstrating sustained technical contributions to industry including publishing well-cited technical papers at conferences and in journals, book chapters, and patents; serving as an editor of a journal or reference book; and being a leader or participant in industry blogs, focus groups, technical roadmaps, newsletters, and forums.

4) Documenting advanced technical recognitions in electronics packaging.

Methods to document technical recognitions include receiving technical awards from a company, institute, professional society, or academic institution; being the acknowledged inventor of a seminal technology or process important to industry; serving as the point person for global high-level task force activity; and being elected to be a Member of an organization such as the US National Academy of Engineering, Royal Academy of Engineering, Chinese Academy of Engineering, IBM Academy of Technology, etc.

5) Provide at least one endorsement letter.

Nominations for the Distinguished Achievement Certificates will be accepted two times per year: Jan 1–June 30 and Aug 30–Oct 31.

# **EPS Distinguished Achievement Certificate for Professional Engagement and Service**

Criteria: Must be a current EPS member

There are four high-level areas of focus for this new certificate. These areas include:

1) Demonstrating leadership in the electronics packaging field.

Leadership and broad impact activities in electronics packaging can be documented from outstanding accomplishments during industry employment or for notable volunteer contributions to the profession and society.

2) Illustrating broad impact/influence in the electronics packaging field.

Examples of significant professional service include serving as an officer in a technical society at the international, national, or local chapter level; participating in packaging related technical committees, councils, or affinity groups; contributing to technology roadmaps such as the Heterogeneous Integration Roadmap (HIR); and receiving a professional society or industry award based on service contributions.

3) Providing extensive service and "give back" to the profession and/or industry; and

Documentation of "give-back" to one's technical community can be accomplished via demonstrations of coaching and mentoring of co-workers, young professionals, and students.

4) Provide at least one endorsement letter.

Nominations for the Distinguished Achievement Certificates will be accepted two times per year: Jan 1–June 30 and Aug 30–Oct 31.

More details on the Certificate Program are available on the EPS website at <a href="https://eps.ieee.org/education/eps-certificate-program.html">https://eps.ieee.org/education/eps-certificate-program.html</a>. The EPS Certificate Program is sponsored by the IEEE EPS VP Education and is offered only to EPS members. For questions, please contact Jeff Suhling (jsuhling@auburn.edu).

#### **EPS Resource Center**

he IEEE EPS Resource Centers contains valuable, technical content from reputable experts to enhance research or industry work, implement trainings, or earn CEU/PDH credits—all of which are universally available on demand.

IEEE EPS Resource Centers benefits include:

- Access to valuable technical community content

- Access to content 24 hours a day, 7 days a week through an easy-to-use global portal

- Available at no cost for EPS members

• Opportunities to earn CEUs and PDHs

Top webinars:

- The Evolution of Lead-Free Solder Alloy

- Powering Heterogeneous Integration: An Overview of the Integrated Power Electronics Chapter of the HIR Roadmap

- Thermal Management Challenges and Opportunities for Heterogeneous Packages

- Overview of the Integrated Photonics Chapter of the Heterogeneous Integration Roadmap

- Advanced Packaging for Autonomous Driving

https://resourcecenter.eps.ieee.org/

$\bigoplus$

JULY 2022 / IFFE ELECTRONICS PACKAGING SOCIETY NEWSLETTER

#### **CONFERENCE NEWS**

# The 72nd ECTC Conference—Back In-Person Submitted by Michael Mayer, Assistant Program Chair, IEEE ECTC 2023

This year's IEEE Electronic Components and Technology Conference (ECTC) saw the return to an in-person event after the previous instances were virtual conferences. ECTC took place once again in San Diego, California, at the rejuvenated Sheraton San Diego Hotel and Marina, from May 31 to June 3, 2022. The conference brought together a total of 1,509 industry professionals, academics, and students in attendance from 24 countries.

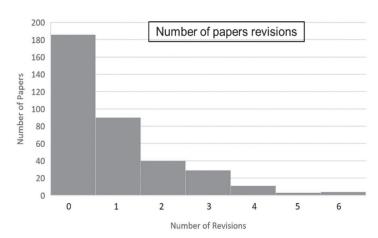

The 72nd ECTC included 362 technical contributions, which were organized into 36 oral sessions and 5 interactive presentation (IP) sessions. There were 9 special sessions. The 16 professional development courses (PDCs) were attended by 337 attendees. The conference had more than 100 exhibitors at the Technology Corner Exhibit, a tribute to the quality of the conference and its attendees. The conference benefited from a strong number of sponsors and sponsorship, further testament to the value delivered by this flagship conference.

Preparations for the 72nd ECTC started last October, when the professional volunteers serving in ECTC's technical subcommittees reviewed a strong number of 488 submitted abstracts. Ultimately, 71% of the submissions were accepted, leading to 362 presentations at the conference. This year, 54% of the submitted abstracts were from corporations, and 46% were from academia and from research institutions. In a testimony to the diversity of the industry and the conference, abstracts were received from 25 countries with the Unites States, Taiwan and South Korea leading the way in number of abstract submissions. Due to travel restrictions, mainly from Asia countries about 1/3 of the papers were presented via a pre-recorded format with written questions sent to the authors directly. Affected also by travel restrictions was our ECTC 2022 General Chair, Rozalia Beica, who over a year of weekly telecoms directed the ExComm resulting in an outstanding conference.

Ten technical subcommittees decided on the conference program at the virtual Technical Program Committee's annual planning meeting on November 5, 2021. The technical subcommittee chairs and session chairs did an excellent job developing interesting sessions and communicating with their session authors, to ensure non-commercial and previously unpublished manuscripts to be ready in time for the conference. The session chairs reviewed

|                           | in person | virtual |

|---------------------------|-----------|---------|

| Technical Sessions        | 162       | 90      |

| Interactive Presentations | 60        | 50      |

| Total                     | 222       | 140     |

Distribution on in person and virtual presentations at the 20222 ECTC.

the submitted manuscripts for quality and novelty and in some cases requested edits prior to final acceptance. ECTC again used the IEEE Computer Society Conference Publishing Services to receive and process manuscripts. As in previous years, the IEEE Cross-Check system was used to ensure that all of the ECTC manuscripts maintain a high level of original content. Over 50% of the papers required at least 1 revision, some had up to 6 revisions.

From Tuesday May 31 to Thursday June 2, we had the pleasure to attend a series of special sessions, special panels, and plenary presentations. As usual, the first day of the conference, the Tuesday following Memorial Day, featured PDCs and a variety of special sessions. This year, the conference had eight morning PDCs, running from 8 a.m. to noon, and another eight afternoon PDCs, running from 1:30 p.m. to 5:15 p.m. The total number of PDC attendees was 334. The courses continued to serve a convenient way for students and engineers to quickly get "up to speed" on the current topics of importance in electronics packaging. A total of 2 PDCs were new, and 1 PCD was virtual.

For the first time, we had the high number of six special event organized on Tuesday. In the morning from 8:30 to 10:00,

72nd ECTC during in-person lunch.

ECTC Special sessions were very well attended.

Chukwudi Okoro—Corning Inc., and Benson Chan – Binghamton University, organized a special session on high volume manufacturing of MicroLED display technology with six invited panelists from Lumiode, PARC, Playnitride, XDisplay, Corning Inc., and Yole Development.

Tuesday morning was also the occasion of the IEEE EPS Heterogeneous Integration Roadmap (HIR) special session from 10:30 am to 12 pm. This session was chaired by Amr Helmy—Univ. of Toronto and Seoung Wook Yoon—Samsung. This activity is organized under the auspices of IEEE EPS.

Next was the special session on chiplet to co-packaged optics from 1:30 pm to 3 pm, chaired by E. Jan Vardaman—TechSearch International, with panelist from Intel, Cisco, Marvell and AMD.

It was followed by the special session on IC substrate evolution towards next generation heterogeneously integrated high performance applications, 3:30 pm to 5 pm, chaired by Kuldip Johal—Atotech Group, and Bora Baloglu—Amkor. Panelist came from Intel, Amkor, AT&S, Ajinomoto Tine-Techno USA, and Atotech.

The ECTC Student Reception, sponsored by Texas Instruments, was held on Tuesday from 5 pm to 6 pm. A steady stream of student attendees took advantage of the opportunity to mingle and network with professionals in the field. Right after this, the General Chair's Speakers Reception was given from 6-7 pm for Speakers and Session Chairs. These receptions provided a great

start to the conference, and helped prepare everyone for the following three days filled with technical presentations and networking opportunities. The Young Professionals Networking Panel and Reception took place from 7 pm to 7:45 pm and was chaired by Yan Liu—Medtronic, and Adel Bajwa – Kulicke and Soffa.

The Tuesday program ended with the EPS President's Panel Session from 7:45 pm to 9:15 pm, chaired by Kitty Pearsall—EPS President and Boss Precision, and Christopher Riso—Booz Allen Hamilton. Panelist were from the Office of the Undersecretary of Defense for Research and Engineering, Intel, and Qorvo.

On Wednesday, we were also able to enjoy an excellent keynote presentation from Chris Koopmans, COO, Marvell. Chris was virtually introduced by Rozalia Beica, the 2022 ECTC General Chair. The presentation focused on cloud-optimized silicon to accelerate data infrastructure. Awards for best and outstanding papers from the virtual 71st ECTC 2021 and the Intel Best Student Paper Award were presented by Allan Hoffman.

The Diversity and Career Growth Panel and Reception was co-organized with ITherm and chaired for ECTC by Kim Yess—Brewer Science, and for ITherm by Christina Amon—University of Toronto. Francoise von Trapp—3D InCites, served as moderator during the panel on Wednesday which lasted from 6:30 pm to 7:30 pm. Panelists were from IBM, Lam Research, Edwards Vacuum, and Cadence.

Texas Instruments Student reception.

Tuesday Luncheon: Keynote speaker and 2021 Best and outstanding papers Awards.

Also on Wednesday, Rozalia Beica—AT&S and General Chair ECTC, organized the plenary session on the digital transformation enabling future growth of semiconductor and advanced packaging, from 7:45 pm to 9:15 pm. Panelist were from Intel, TSMC, Yole Development, Onto Innovation, Samsung, and Atotech.

On Thursday from 8 pm to 9:30 pm, the EPS Seminar took place about interconnect technologies for chiplets, chaired by Yasumitsu Orii—Nagase and Shigenori Aoki—Lintec. Panelists were from Intel, IBM, Unimicron, TSMC, SPIL, and Furukawa Electric.

Each day at ECTC begins with the Speakers Breakfast in which the presenters and session chairs meet and take care of the preparatory work for their respective sessions. The PDC Chair, Kitty Pearsall, provided instructions to the PDC instructors and proctors on Tuesday morning, and Karlheinz Bock, the Program Chair, hosted these breakfast meetings.

Wednesday marks the start of the technical sessions with six sessions running in parallel throughout each of the three days. Each oral session featured seven paper presentations, and the interactive presentation sessions featured between15 and 25 papers. Wednesday morning started with large crowds in the six sessions with titles "Advanced Packaging for Heterogeneous Integration and High-Performance Computing", "High Performance Dielectric Materials for Advanced Packaging", "Antenna-in-Package for Communication, Radar and Energy Transfer", and "Hybrid Bonding and Innovations for 3D Integration", "Bonding Technol-

ogy: Novel Assembly Methods and Processes", and "Emerging Modeling Including AI and Machine Learning". In parallel, the first of five interactive sessions took place from 9–11 am, with 25 paper presentations. High session attendance was noted also after the keynote luncheon in the afternoon sessions, with the topics "Advanced Flip Chip and Embedded Substrate Technologies", "Hybrid and Direct Bonding Development and Characterization", "Millimeter-Wave Antenna-In-Package: Design, Manufacturing and Test", "Novel Photonics Packaging Technology", "Automotive and Harsh Environment", and "Manufacturing and Assembly Process Modeling". Again in parallel, the second interactive session took place from 2–4 pm, with 23 paper presentations. Attendees rated all oral and interactive session paper ratings only through the ECTC mobile app "Whova".

The Thursday morning sessions were well attended and covered the topics "Technologies for Heterogeneous Integration, Automotive and Power Electronics", "Novel Bonding and Stacking Technologies", "Enhanced Methods & Processes for Heterogeneous Integration Assembly", "Hybrid & Direct Bonding Innovation, Optimization & Yield Improvement", "Novel Characterization Techniques and Test Methods", and "Flexible, Wearable Sensors and Electronics". Thursday afternoon included the sessions "Advances in Fan-Out Panel Level Packaging", "Enhancements in Fine-Pitch Interconnects, Redistribution Layers and Through-Vias", "Millimeter-Wave RF Components and Modules for 5G", "AI, Quantum Computing and Novel 3D Packaging Solutions",

Speaker Breakfast and Technical Sub-committees.

ECTC Interactive Presentations.

Thursday EPS Luncheon presented Best Transactions paper, Best Editors, New IEEE Fellows and Major Awards.

Network opportunities at the ECTC.

# **Best Session Paper**

Proof of Concept: Glass-Membrane Based Differential Pressure Sensor

Anatoly Glukhovskoy, Maren S. Prediger, Jennifer Schäfer—Leibniz University; Norbert Ambrosius, Aaron Vogt, Rafael Santos, Roman Ostholt—LPKF Laser & Electronics AG; Marc Christopher Wurz—Leibniz University

### 2) Best Interactive Presentation Paper

System in Package Embedding III-V Chips by Fan-Out Wafer Level Packaging for RF Applications

Arnaud Garnier, Laetitia Castagné, Florent Gréco— CEA-Leti; Thomas Guillemet—Thales DMS; Laurent Maréchal, Mehdy Neffati—United Monolithic Semiconductors; Rémi Franiatte, Perceval Coudrain—CEA-Leti; Stéphane Piotrowicz—III-V Lab; Gilles Simon—CEA-Leti

#### 3) Outstanding Session Paper

Ultra-Thinning of 20-nm Node DRAMs Down to 3 µm for Wafer-on-Wafer (WOW) Applications

Zhiwen Chen, Naoko Araki, Youngsuk Kim, Tadashi Fukuda, Koji Sakui, Tomoji Nakamura - Tokyo Institute of Technology; Tatsuji Kobayashi, Takashi Obara—Micron Memory Japan; Takayuki Ohba—Tokyo Institute of Technology

#### 4) Outstanding Interactive Presentation Paper

Cu-Recrystallization and the Formation of Epitaxial and Non-Epitaxial Cu/Cu/Cu Interfaces in Stacked Blind Micro Via Structures Tobias Bernhard, S. Dieter, Roger Massey, S. Kempa, E. Steinhäuser, Frank Brüning—Atotech Deutschland GmbH

#### 5) Intel Best Student Session Paper

Mechanical Behavior and Reliability of SAC+Bi Lead Free Solders with Various Levels of Bismuth KM Rafidh Hassan, Jing Wu, Mohammad S. Alam, Jeffrey Suhling, and Pradeep Lall—Auburn University

"Advanced Processes for Manufacturing and Yield Enhancement", and "Thermal Management and Warpage Analysis of Highly Integrated Packages".

The IEEE Electronics Packaging Society President, Kitty Pearsall, presided over the luncheon on Thursday and presented the EPS Society Awards and introduced the society new Fellows. The recipients were presented with a certificate and warm applause from the audience.

The ECTC 2022 Technical Program Committee meeting was held on Thursday at 5:30 p.m. Florian Herrault, who will serve as the Program Chair for ECTC 2023, chaired this meeting and presented the statistics of the 72nd ECTC and the timeline for the run up to the 73rd ECTC that is planned to be held in Orlando next year. Florian Herrault also introduced Michael Mayer of the University of Waterloo as the Assistant Program Chair of the 73rd ECTC. This meeting also enabled the ECTC technical program subcommittees to get in touch with potential new members of their committees.

The Gala Reception on Thursday evening was the highlight of the week for the conference attendees, exhibitors, sponsors, and their guests. It was setup outside between San Diego bay and the hotel, in the shade of large trees. It was a time to celebrate the success of the ECTC by socializing and enjoying the excellent food and beverages that were supported by the Gala Reception Gold and Silver sponsors.

# **2021 ECTC Best Paper Awards**

Friday morning sessions were also well attended, covering the topics "Advancements in 2.5D and 3D Packaging Technology", "Soldered and Sintered Interconnections", "Interconnection Reliability", "Packaging Assembly: Solder, Sintering, and Thermal Interface Materials", "Materials and Processes for Fan-Out and Advanced Packaging", and "High-Speed Challenges in Power and Signal Integrity". Friday afternoon included the sessions "Fan-Out Packaging Technologies and Applications", "Advanced Interconnect and Wire Bond Technologies for Flexible Device Applications", "Advanced Reliability Modeling and Characterization", "Processing Enhancements in Fan-Out and Heterogeneous Integration", "Packaging with Additive Manufacturing for Harsh Conditions", and "Modeling and Characterization of Interfaces and Interconnects".

The Technology Corner exhibit area hosted more than 100 exhibitors. Exhibitors had multiple resources available within their virtual booth, offering virtual introductions, brochure materials, staff contact information, and an opportunity to submit inquiries and discuss directly with exhibit members.

Friday Luncheon and Raffle process presented by their sponsors.

ECTC Technology Corner.

Overall, the 72nd ECTC was an inspiring experience making us realize what we had lost during the two years of virtual ECTCs. The in-person participation energizes many of us in a way the online meetings cannot. The strength of the packaging community manifested itself by the relatively high number of attendees given the fact that several organizations still were restricting travel of their employees. We also had a very strong exhibitor presence, excellent sponsorship, and many high-quality technical presentations with excellent presentation attendance. The ECTC Executive Committee sincerely thanks all the attendees, exhibitors, and conference sponsors for their support as well as all the committee members and chairs who are volunteering their time to help organize the sessions and make ECTC such a success every year. Very

special thanks also to our excellent event management team for bringing back the in-person reality flawlessly. See all the conference pictures at Flicker and keep in touch with the ECTC through LinkedIn.

The 73rd ECTC will be held at The JW Marriott Orlando Grande Lakes, Orlando, Florida, USA, May 30–June 2, 2023. Ibrahim Guven from Virginia Commonwealth University will be the General Chair of this conference. The Call for Papers and PDC Proposals will be available at www.ectc.net, and the abstract submission will close on October 10, 2022. So get those abstracts ready and submit them as soon as abstract submission opens.

See you all in Orlando in 2023!

IEEE ELECTRONICS PACKAGING SOCIETY NEWSLETTER / JULY 2022

# IEEE Electronics Packaging Society (EPS) Malaysia Chapter

IEEE IEMT 2022 invites you to submit your work to the 39th IEMT 2022 that will be held in Le Meridian, Putrajaya, Malaysia. It is an international event organized by the IEEE-EPS, Malaysia Chapter, with cosponsorship from IEEE Electronic Packaging Society (EPS). The IEMT typically attracts more than 400 attendees over

the world. The last IEMT 2018 (Melaka, Malaysia) hosted 600 attendees, with 100 accepted papers and interactive presentation featured in 16 sessions. IEMT 2022 welcomes papers covering electronics packaging technology in diverse semiconductor market. This segment includes telecommunication, data center, automotive, EV, healthcare, aerospace, defense and others.

[https://www.iemt.com.my/]

# **Scope of Papers Solicited**

Abstract should include original and previously unpublished, non-confidential and non-commercial information on new developments, technology and knowledge in the areas including, but not limited to those given below.

- Advanced Packaging—2D, 2.5D, 3.0D, Chiplets, WLCSP, FOWLP, FOPLP & HI

- Thermal/Mechanical/Electrical Simulation & Characterization

- Material & Processing

- Emerging Packaging—Opto, Medical, Nano Technology, Wearable Electronics

- Interconnections Technologies—TSV,  $\mu$ -bump, hybrid bond, FC and embedded

- LED, MEMS, NEMS & Sensor Packaging & IoT

- IC Testing Technology

- Surface Mount Technology

- Quality, Reliability & Failure Analysis

- High-Speed, Wireless & Components

# **Keynote Speakers**

**Prof. Chris Bailey**Director of Computational Mechanics and Reliability Group

University of Greenwich

Mr Chew CH Senior Director OnSemi

Mr Terrence Tan

Senior Principal Engineer,

Manufacturing and Product

Engineering

Intel

**Dr.Veer Dhandapani** Senior Director of Product Development NXP Semiconductors

Mr. Laurent Herard Group VP—Head of Back End Manufacturing and Technology R&D STMicroelectronics

Bernhard Knot Head of Backend Innovation Infineon

E. Jan Vardaman

President and Founder of

TechSearch International, Inc

Rolf Aschenbrenner

Deputy Director and Head

of SIIT

Department

Fraunhofer Institute (IZM)

https://www.iemt.com.my/program/iemt2022-keynotes/

# **Conference Registration**

IEMT 2022—39th International Electronics Manufacturing Technology Conference 2022

#### Scan & Share

Scan the qr to open and share in mobile, or Click Here (1) to copy the shareable link http://t2u.asia/e/26660

http://t2u.asia/e/26660

If you have any questions, contact:

Conference Secretariat

E-mail: iemtmalaysia@gmail.com

Conference Web: https://www.iemt.com.my/

# **Top Conference Papers Based on Usage**

# **2021 IEEE 71st Electronic Components and Technology Conference (ECTC)**

(June 1–July 4, 2021)

Wafer Level System Integration of the Fifth Generation CoWoS®-S with High Performance Si Interposer at 2500 mm<sup>2</sup> P. K. Huang; C. Y. Lu; W. H. Wei; Christine Chiu; K. C. Ting; Clark Hu; C.H. Tsai; S. Y. Hou; W. C. Chiou; C. T. Wang; Douglas Yu

# Die Embedding Challenges for EMIB Advanced Packaging Technology

Gang Duan; Yosuke Kanaoka; Robin McRee; Bai Nie; Rahul Manepalli

# Heterogeneous Integration of a Compact Universal Photonic Engine for Silicon Photonics Applications in HPC

H. Hsia; C.H. Tsai; K.C. Ting; F.W. Kuo; C.C. Lin; C.T. Wang; S.Y. Hou; W.C. Chiou; Douglas C.H. Yu

# InFO\_oS (Integrated Fan-Out on Substrate) Technology for Advanced Chiplet Integration

Y. P. Chiang; S. P. Tai; W.C. Wu; John Yeh; C. T. Wang; Douglas C. H. Yu

# SoIS- An Ultra Large Size Integrated Substrate Technology Platform for HPC Applications

Jiun Yi Wu; Chien-Hsun Chen; Chien-Hsun Lee; Chung-Shi Liu; Douglas C. H. Yu

# 2021 20th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm)

(June 1-4, 2021)

# The effectiveness of heat extraction by the drain metal contact of $\beta\text{-}Ga2O3$ MOSFETs

Samuel H. Kim; Daniel Shoemaker; Bikramjit Chatterjee; Kelson D. Chabak; Andrew J. Green; Kyle J. Liddy; Gregg H. Jessen; Samuel Graham; Sukwon Choi

### Hybrid Two-Phase Cooling Technology For Next-Generation Servers: Thermal Performance Analysis

Raffaele L. Amalfi; Francois P. Faraldo; Todd Salamon; Ryan Enright; Filippo Cataldo; Jackson B. Marcinichen; John R. Thome

Package-Level Integration of Liquid Cooling Technology with Microchannel IHS for High Power Cooling

Je-Young Chang; Devdatta Kulkarni; Ravi Mahajan; Michael Jorgensen; Nick Neal; Rich Dischler; Aravind Dasu; Sandeep Ahuja; Rajiv Mongia

Hybrid Electric Aircraft Thermal Management: Now, New Visions and Future Concepts and Formulation

Terry J. Hendricks; Calin Tarau; Rodger W. Dyson

Heat Spreading and Heat Removal Needs of a Novel Power Electronics Package with Integrated Cooling

Ahmet Mete Muslu; Ryan Wong; Vanessa Smet; Yogendra Joshi

**2021 IEEE 23rd Electronics Packaging** Technology Conference (EPTC)

(December 1-30, 2021)

High Reliability Solution of 2.5D Package Technologies

Hsin Jou Lin; Vito Lin; Joe Lin; Ying Ju Lu; David Wang; Yu Po Wang

# Cu CMP Dishing in High Density Cu Pad for Fine Pitch Wafer-to-Wafer (W2W) Hybrid Bonding

HongMiao Ji; King-Jien Chui

EPTC 2021 Invited Technology Talk: Roadmap Based on Holistic Understanding of Thermo-Mechanical Challenges from Package to System to Maximize Silicon Performance

Gamal Refai-Ahmed; Suresh Ramalingam; Tahir Cader; Jason Strader; Jari Huttunen; Anthony Torza; Srikanth Rangarajan; Bahgat Sammakia; Vadim Gektin; Hussam Kabbani