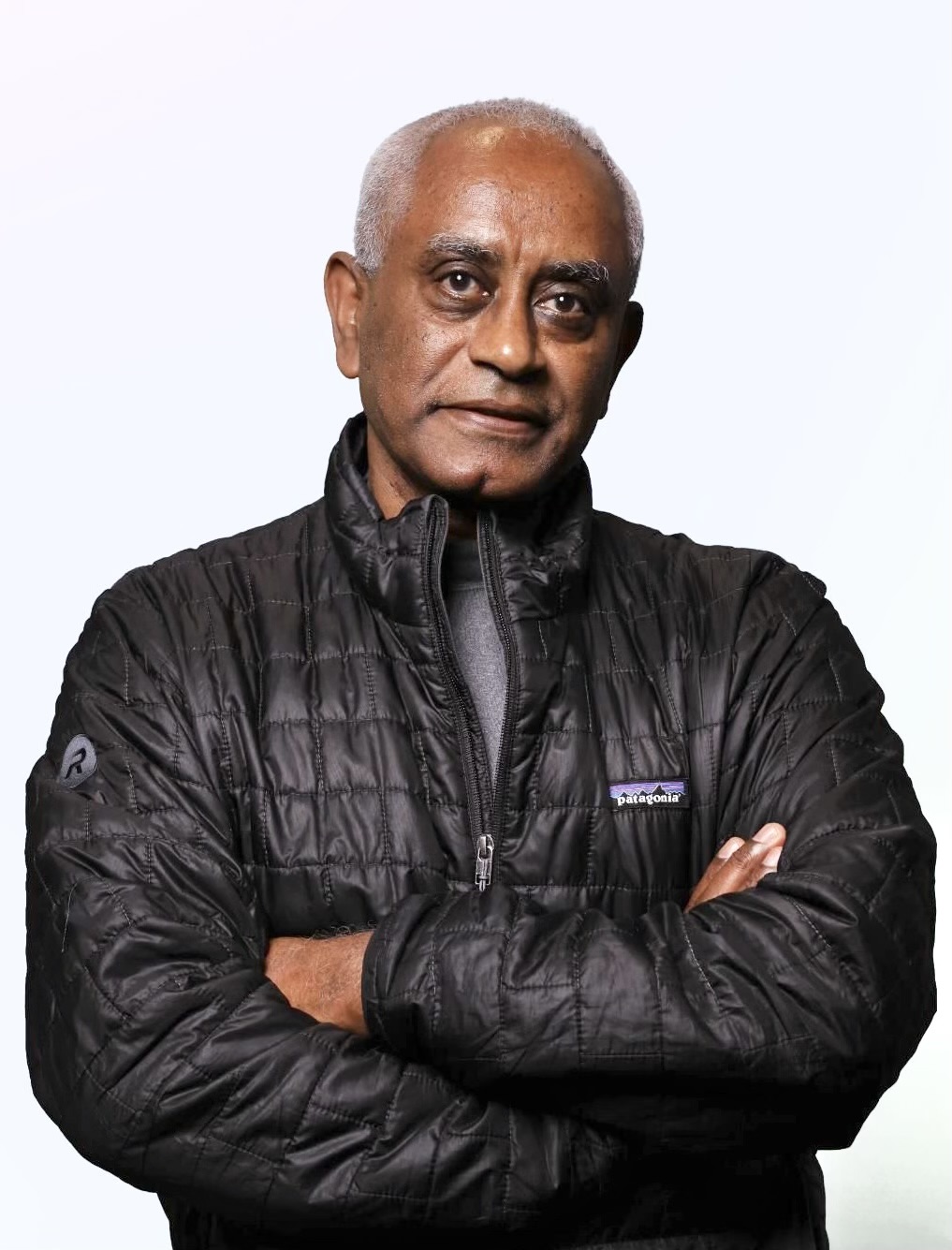

Wendem T. Beyene Bio

Email: wendem@gmail.com

Topics: Design and SI/PI Analysis of High-Performance Memory Systems; Package Requirements for Data Rates of 112 Gbps and Beyond; Modeling and Analysis of heterogeneous interfaces; Applications of Machine Learning to Signal and Power Integrity Problems; Electrical Signaling—Modulation, Equalization, and Channel Design; Statistical Link Modeling and Simulation

Dr. Wendem Tsegaye Beyene has been employed, in the past, by IBM, Hewlett-Packard, and Agilent Technologies, Rambus, and Intel. He has been responsible for end-to-end signal and power integrity analysis of low-power SoC, Memory, CPU and FPGA including fabric and high-speed I/O subsystems as well as I/O modeling. He is currently an Analog & Mixed Signal Architect in Reality Labs at Meta Platforms.

Dr. Beyene, an IEEE fellow, has authored or co-authored numerous refereed publications. These publications covered various disciplines including die, package and system interconnect modeling and simulation, noise and jitter analysis, and optimization as well as machine learning.

He is currently a Senior Area Editor of IEEE Trans. on CPMT and serving as a Distinguished Lecturer for IEEE EPS society. He is also an elected Associate Fellow of the Ethiopian Academy of Sciences. He has organized the annual IEEE EPS conference, DTMES, since 2022, in Ethiopia, Africa.